I/O Registers

www.ti.com

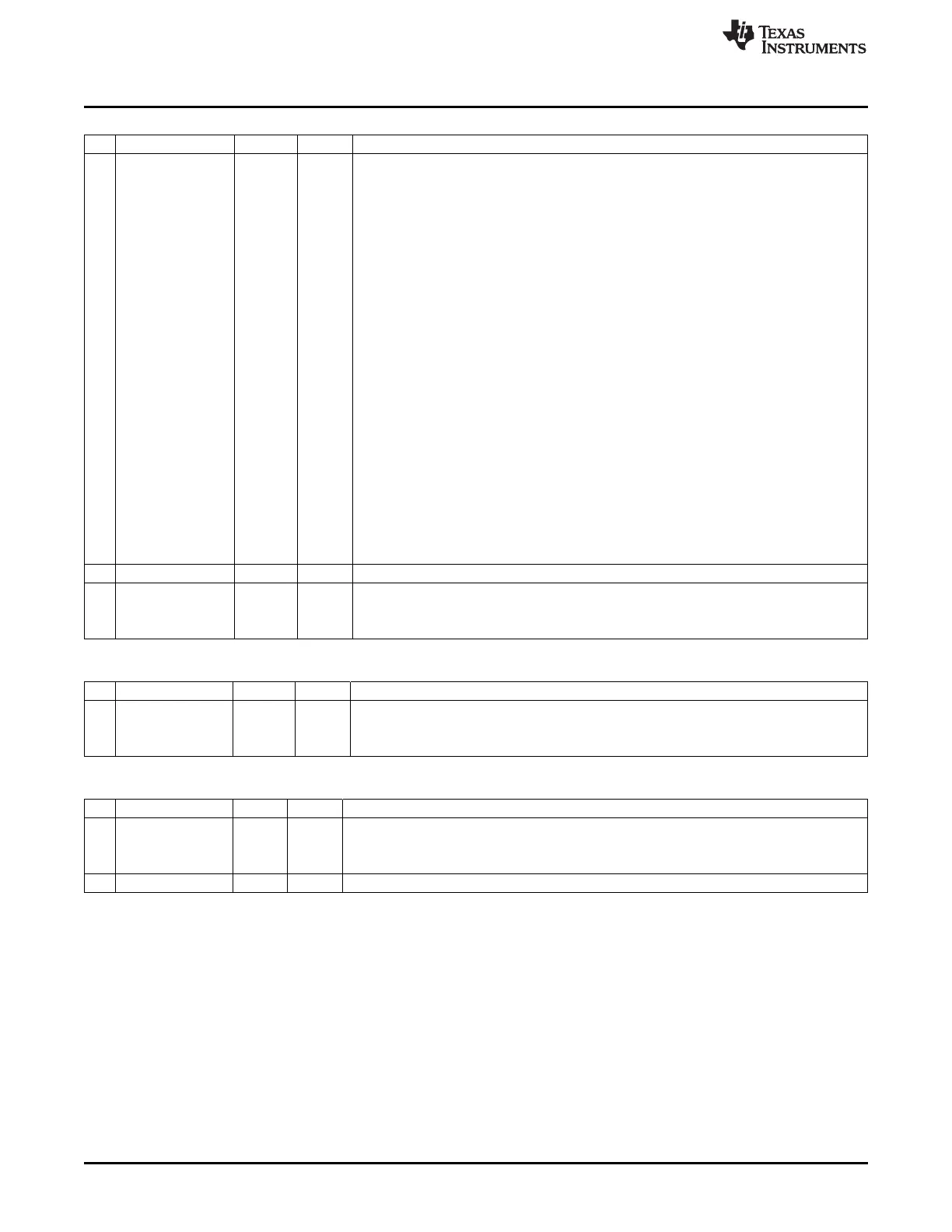

P2DIR (0xFF) – Port 2 Direction and Port 0 Peripheral Priority Control

Bit Name Reset R/W Description

7:6

PRIP0[1:0]

00 R/W Port 0 peripheral priority control. These bits determine the order of priority in the case

when PERCFG assigns several peripherals to the same pins.

Detailed priority list:

00:

1st priority: USART 0

2nd priority: USART 1

3rd priority: Timer 1

01:

1st priority: USART 1

2nd priority: USART 0

3rd priority: Timer 1

10:

1st priority: Timer 1 channels 0-1

2nd priority: USART 1

3rd priority: USART 0

4th priority: Timer 1 channels 2-3

11:

1st priority: Timer 1 channels 2-3

2nd priority: USART 0

3rd priority: USART 1

4th priority: Timer 1 channels 0-1

5 – 0 R0 Reserved

4:0

DIRP2_[4:0]

0 0000 R/W P2.4 to P2.0 I/O direction

0: Input

1: Output

P0INP (0x8F) – Port 0 Input Mode

Bit Name Reset R/W Description

7:0

MDP0_[7:0]

0x00 R/W P0.7 to P0.0 I/O input mode

0:

Pullup/pulldown [see P2INP (0xF7) – Port 2 input mode]

1: 3-state

P1INP (0xF6) – Port 1 Input Mode

Bit Name Reset R/W Description

7:2

MDP1_[7:2]

0000 00 R/W P1.7 to P1.2 I/O input mode

0:

Pullup/pulldown [see P2INP (0xF7) – Port 2 input mode]

1: 3-state

1:0 – 00 R0 Reserved

90

I/O Ports SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...