USER’S MANUAL__________________________________________________________________

38 __________________________________________________________________ M211322EN-D

range/velocity ambiguity resolution or pulse compression for low power

TWT systems.

0916-010

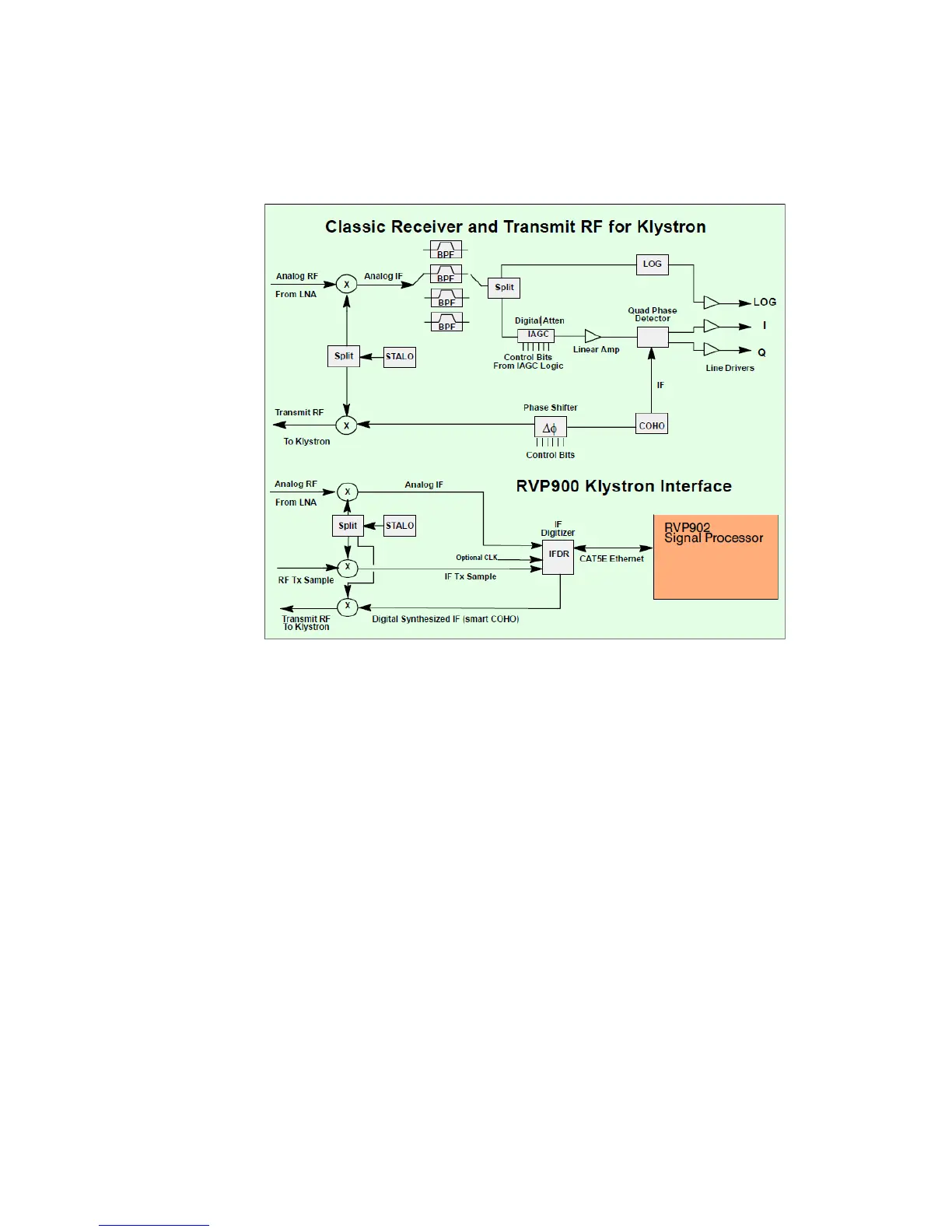

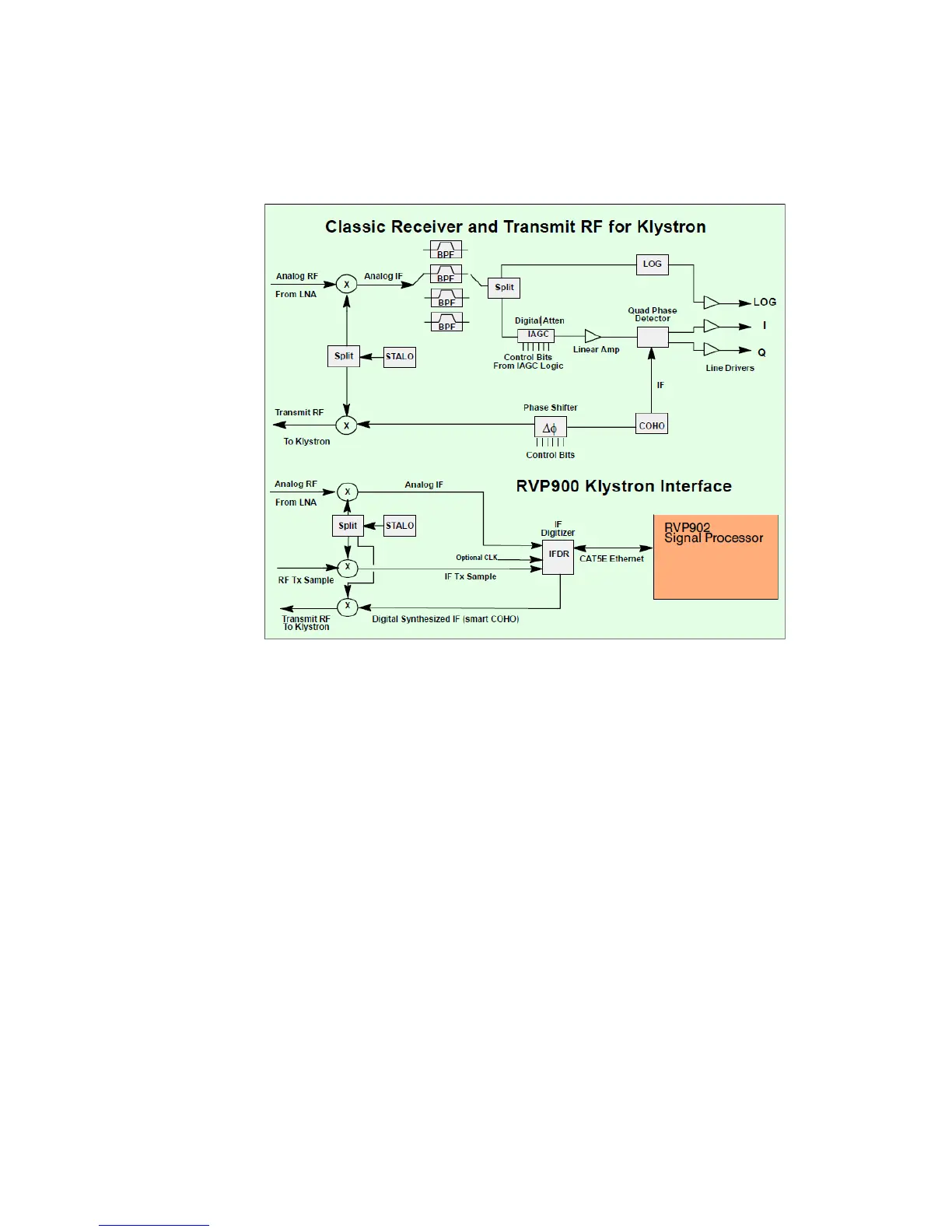

Figure 11 Analog vs Digital Receiver for Klystron Systems

2.8 RVP900 IF Signal Processing

2.8.1 IFDR Data Capture and Timing

The RVP900 design concept is to provide a next generation signal

processor on a single board. The architecture is bus-less and processor

independent. The design relies on common networking components as the

interface for extension and communication.

The digitized IF and burst pulse samples are multiplexed onto the fiber

channel link, which provides the digital data to the RVP902/main board at

approximately 540 Mbps. The 14-bit samples are encoded for transmission

over a fiber channel link. This optical link allows the IFDR to be as far as

100 m away from the RVP902/main board, and provides an added degree

of noise immunity and isolation.

Loading...

Loading...