Chapter 3 _______________________________________________________ Hardware Installation

VAISALA_______________________________________________________________________ 91

First configure the IFD pins themselves. Pins 1 and 24 are power supply

grounds, and are connected with wirewrap wire to the nearby ground posts.

Pins 2 and 3 supply +5 V and +24 V to the STALO, and should be wire

wrapped to the internal power posts. The STALO and DAFC power, are

then supplied externally through the terminal block on the DAFC.

Sixteen jumpers should be installed to connect the Control and Status lines,

that is, pins 4, 6–13, 18–23, and 25. We use pinmap uplink protocol, so H3

and H4 are removed; and a x1 on-board crystal, so H2 is also removed.

The STALO has an output frequency range from 5200 MHz to 6020 MHz

in 100 KHz steps. In this example, we assume that we need an AFC

frequency span of 5580 MHz to 5600MHz. This can be done with the

following setups from the Mb section:

AFC span– [-100%,+100%] maps into [ 3800 , 4000 ]

AFC format– 0:Bin, 1:BCD, 2:8B4D: 0, ActLow: NO

AFC uplink protocol– 0:Off, 1:Normal, 2:PinMap : 2

We map the AFC interval into the numeric span 3800–4000, and choose

the "Bin" (simple binary) encoding format. The actual frequency limits,

therefore, match the desired values:

5200MHz + ( 3800 × 100KHz ) = 5580MHz

5200MHz + (4000 × 100KHz ) = 5600MHz

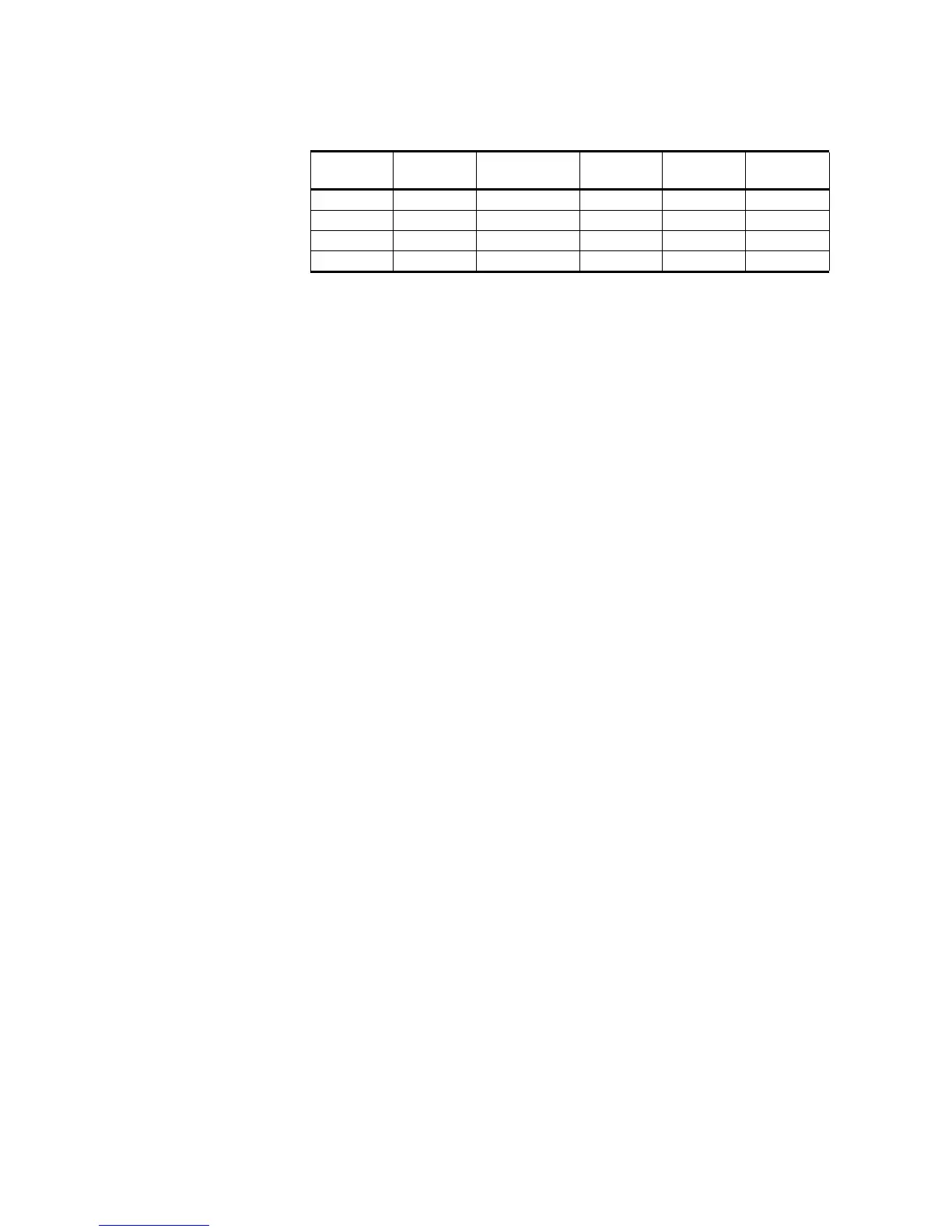

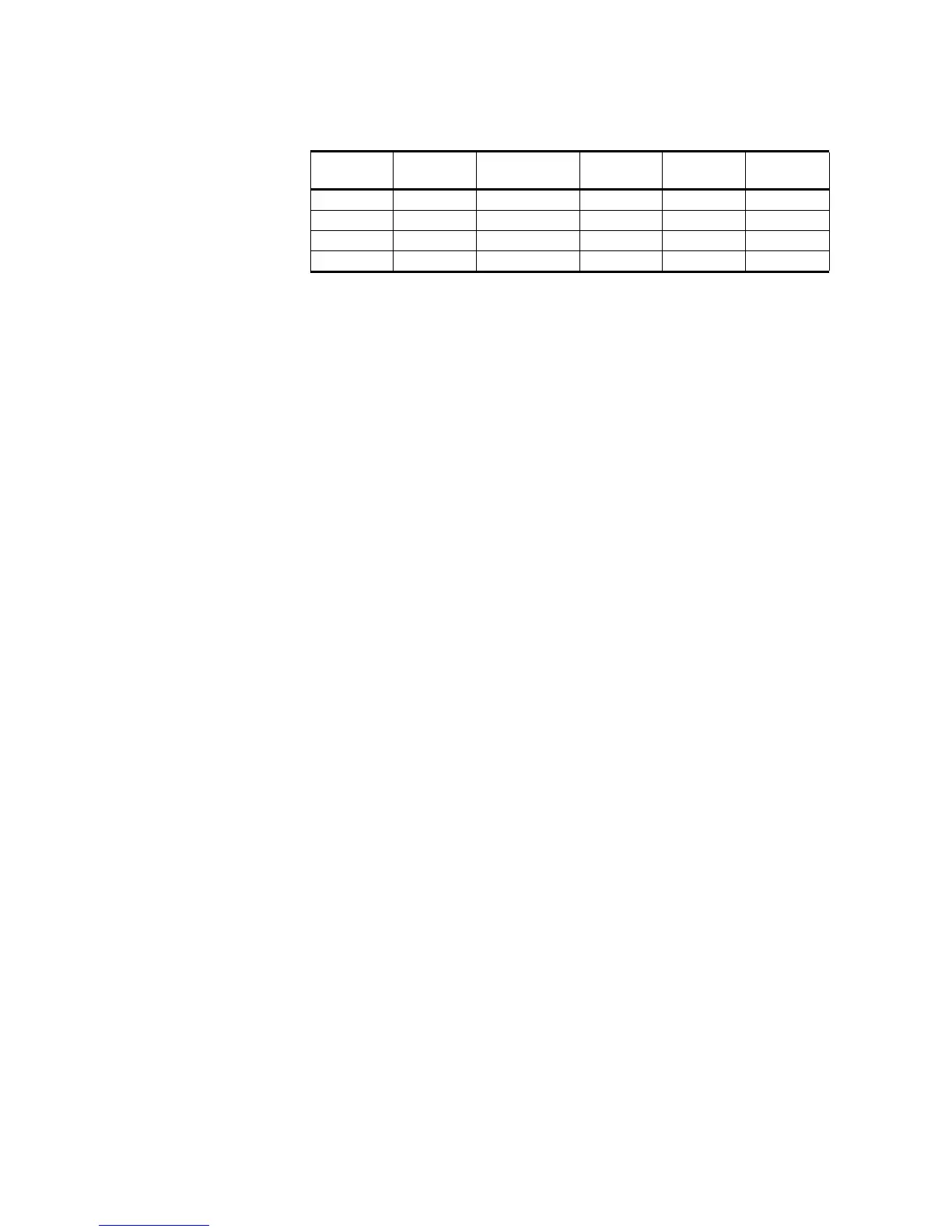

19 10 Bit-8 20 23 Bit-6

21 11 Bit-7 22 24 Ground

23 12 Bit-12 24 25 Bit-13

25 13 Inhb 26 -- --

PinMap Table (Type 31 for GND, 30 for +5)

Pin01:GND Pin02:GND Pin03:GND Pin04:GND Pin05:GND

Pin06:02 Pin07:03 Pin08:11 Pin09:09 Pin10:08

Pin11:07 Pin12:12 Pin13:GND Pin14:GND Pin15:GND

Pin16:GND Pin17:GND Pin18:00 Pin19:01 Pin20:10

Pin21:04 Pin22:05 Pin23:06 Pin24:GND Pin25:13

FAULT status pin (0:None): 4, ActLow: NO

Table 6 Pinout for the CTI MVSR-xxx STALO (Continued)

Ribbon

Pin

"D" Pin Function Ribbon

Pin

"D" Pin Function

Loading...

Loading...