42 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

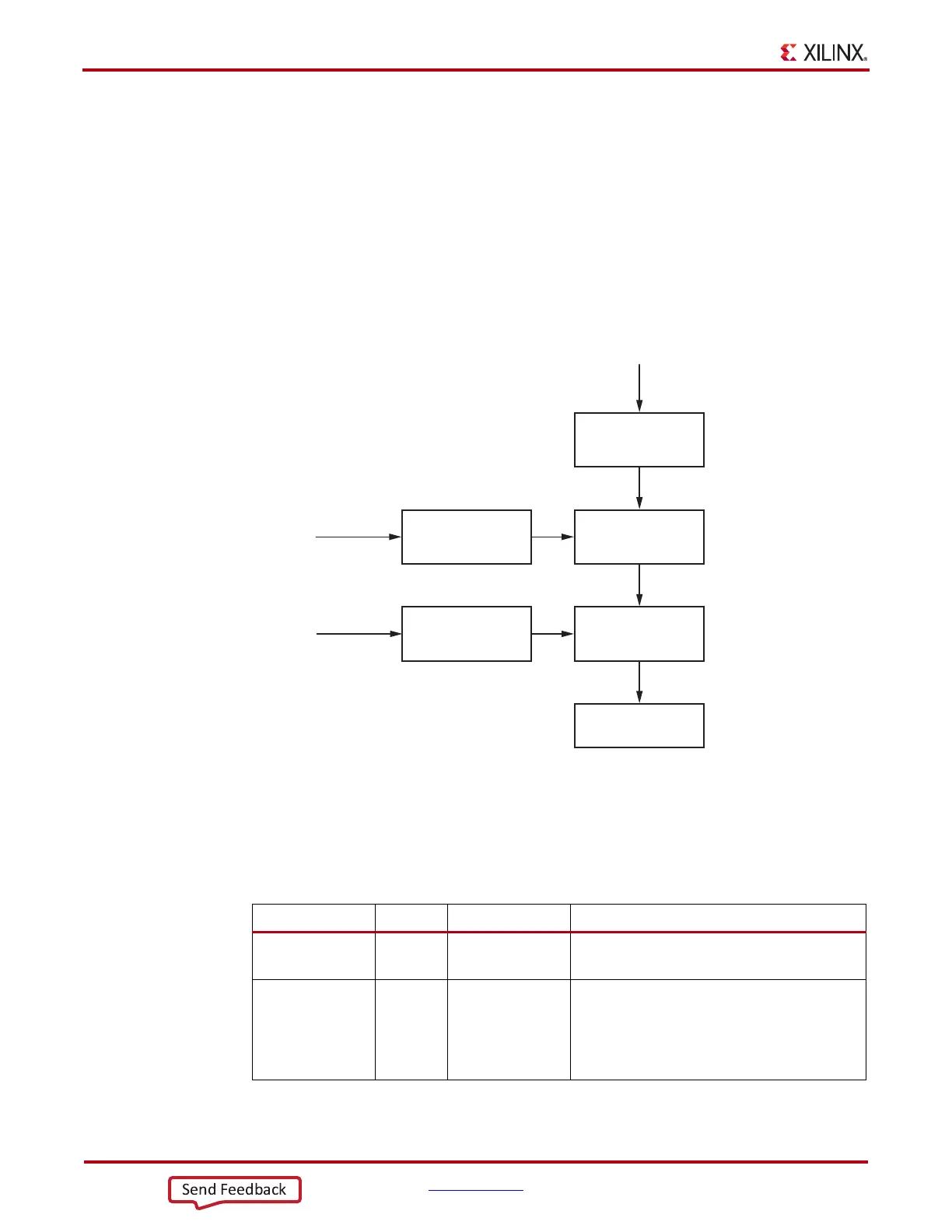

The initializing TX must use GTTXRESET in sequential mode. Activating the GTTXRESET input

can automatically trigger a full asynchronous TX reset. The reset state machine executes the reset

sequence, as shown in Figure 2-13, covering the whole TX PMA and TX PCS. During normal

operation, when needed, sequential mode allows the user to reset TX from activating

TXPMARESET and continue the reset state machine until TXRESETDONE transitions from Low

to High.

The TX reset state machine does not reset the PCS until TXUSERRDY is detected High. The user

should drive TXUSERRDY High after these conditions are met:

1. All clocks used by the application including TXUSRCLK/TXUSRCLK2 are shown as stable or

locked when the PLL or MMCM is used.

2. The user interface is ready to transmit data to the GTP transceiver.

Ports and Attributes

Table 2-14 lists ports required by TX initialization process.

X-Ref Target - Figure 2-13

Figure 2-13: GTP Transceiver TX Reset State Machine Sequence

WAIT Until

GTTXRESET From

High to Low

TXPMARESET

Process

GTTXRESET

High

TXPMARESET

High

TXPCSRESET

Process

TXPCSRESET

High

Sequence Mode & TXUSERRDY

TXRESETDONE

High

WAIT Until

TXPMARESET

From High to Low

WAIT Until

TXPCSRESET

From High to Low

UG482_c2_113_020713

Table 2-14: TX Initialization and Reset Ports

Port Dir Clock Domain Description

GTTXRESET In Async This port is driven High and then deasserted to

start the full TX reset sequence.

TXPMARESET In Async This port is used to reset the TX PMA. It is

driven High and then deasserted to start the TX

PMA reset process. In sequential mode,

activating this port resets both the TX PMA and

the TX PCS.

Loading...

Loading...