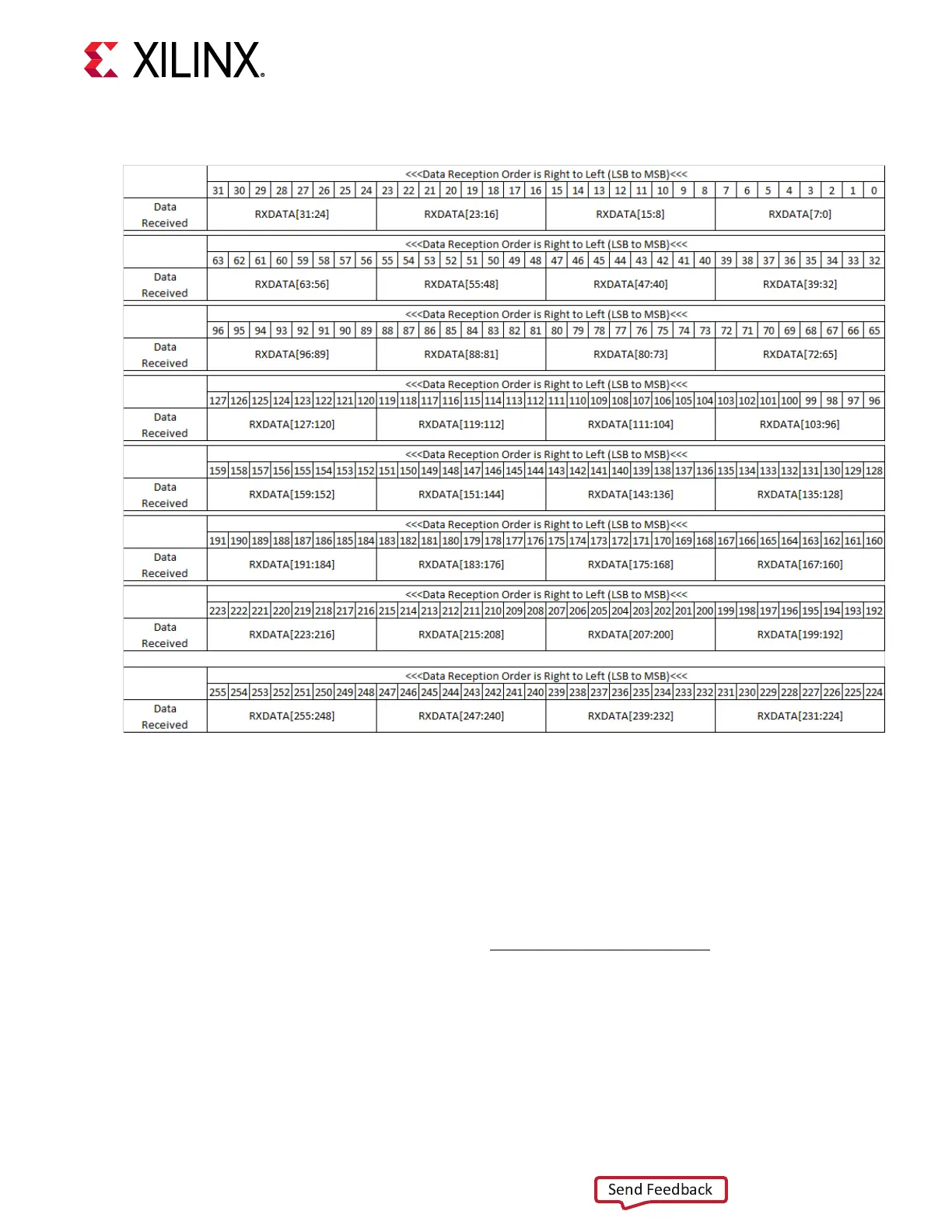

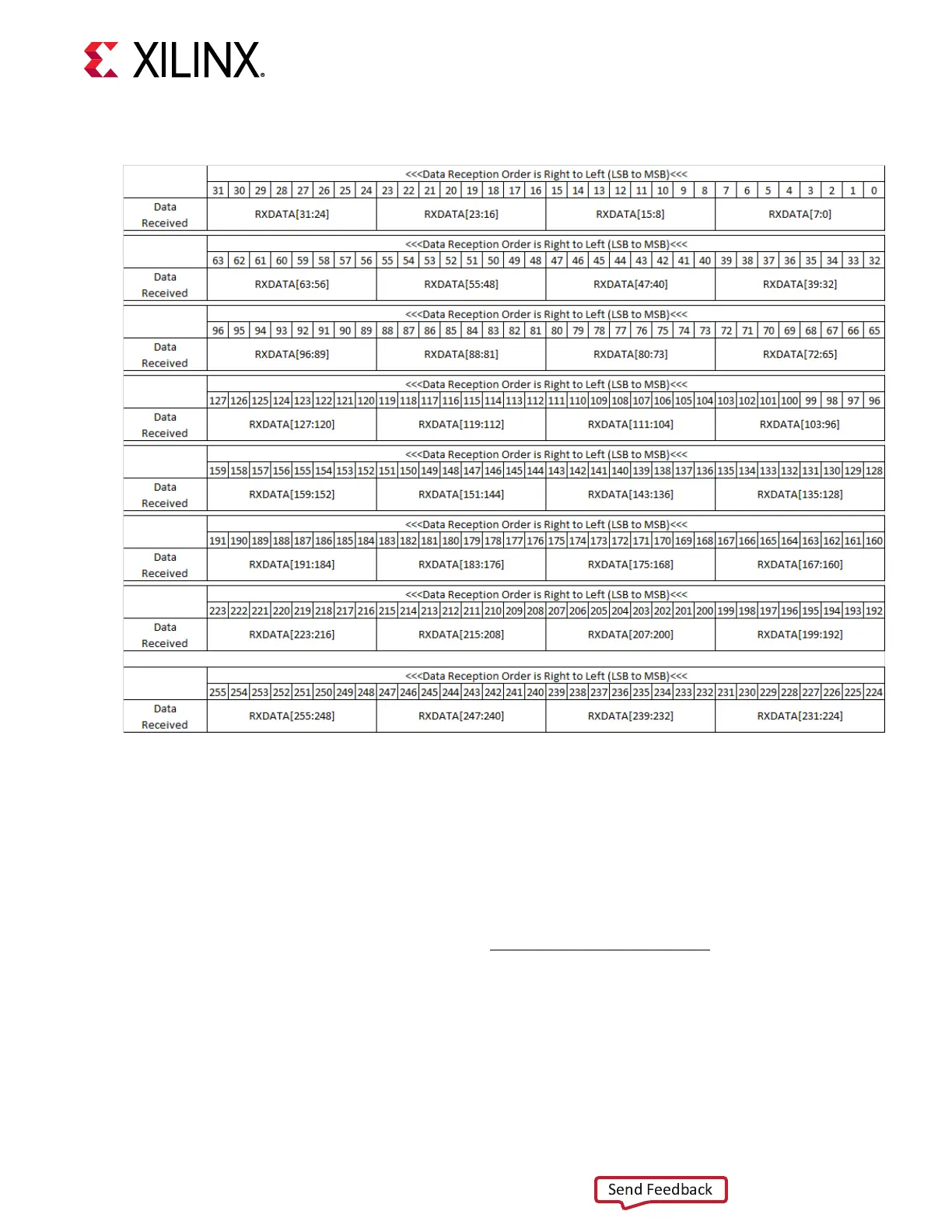

Figure 45: RX Data Received

RXUSRCLK and RXUSRCLK2 Generation

The RX interface includes two parallel clocks: RXUSRCLK and RXUSRCLK2. RXUSRCLK is the

internal clock for the PCS logic in the GTM transmier. The required rate for RXUSRCLK

depends on the internal datapath width of the GTM_DUAL primive and the RX line rate of the

GTM transmier. The following equaon shows how to calculate the required rate for

RXUSRCLK for all cases.

RXUSRCLK Rate =

Line Rate

Internal Datapath Width

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 114

Loading...

Loading...