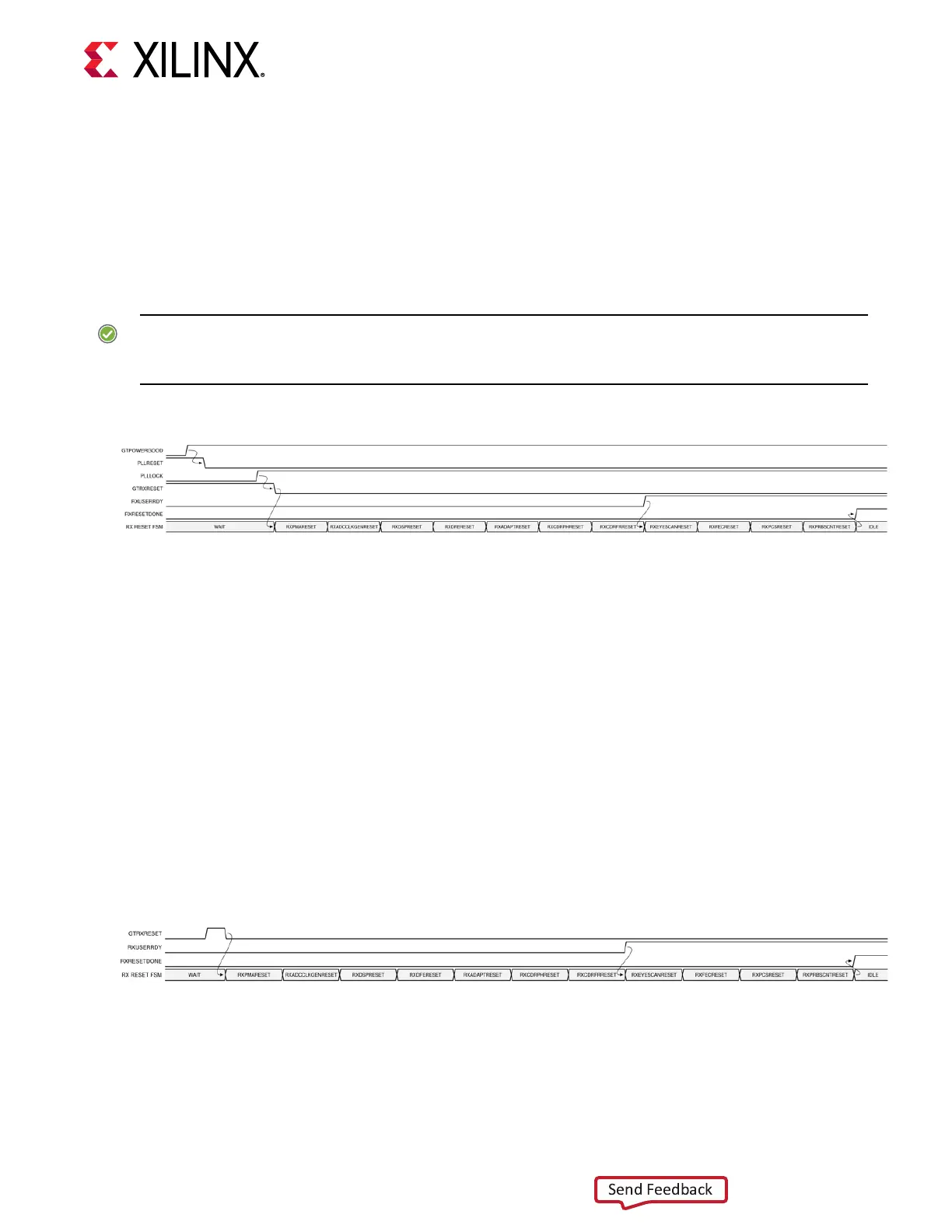

If the reset mode is defaulted to single mode, then you must:

1. Change reset mode to Sequenal mode.

2. Change all RXPMARESETMASK and RXPCSRESETMASK bits to High.

3. Wait another 300–500 ns.

4. Assert PLLRESET and GTRXRESET following the reset sequence described in the following

gure.

RECOMMENDED: Use the associated PLLLOCK from the LCPLL to release GTRXRESET from High to

Low. The RX reset state machine waits when GTRXRESET is detected High and starts the reset

sequence unl GTRXRESET is released Low.

Figure 19: GTM Receiver Initialization after Configuration

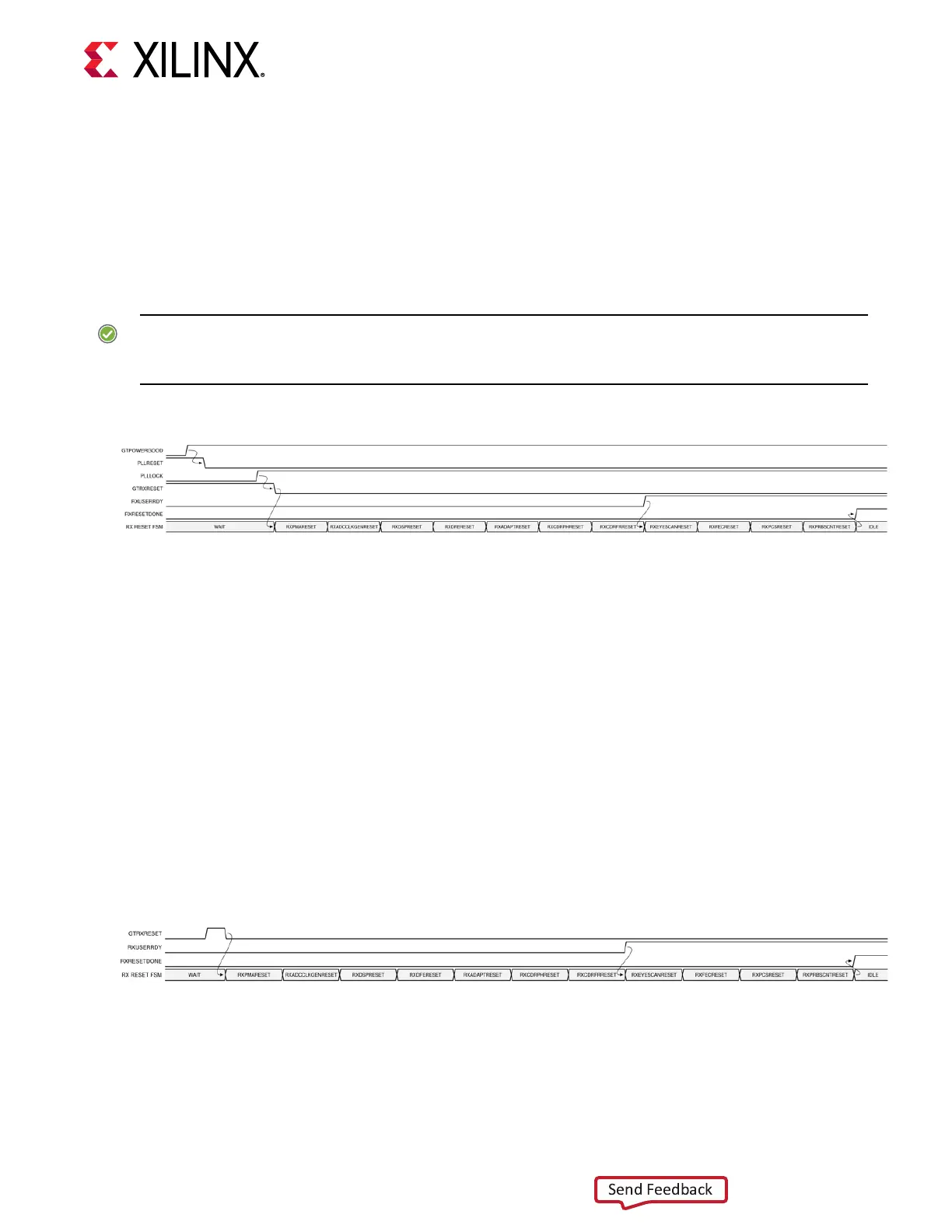

GTM Transceiver RX Reset in Response to GTRXRESET

Pulse in Full Sequential Mode

The GTM transceiver allows you to reset the enre RX at any me by sending GTRXRESET an

acve High pulse. These condions must be met when using GTRXRESET:

1. RXRESETMODE must be set to use sequenal mode.

2. All RXPMARESETMASK and RXPCSRESETMASK bits shold be held to High during the reset

sequence before RXRESETDONE is detected High.

3. The associated PLL must indicate locked.

4. The guideline for this asynchronous GTRXRESET pulse width is one period of the reference

clock.

Figure 20: GTM Receiver Reset after GTRXRESET Pulse in Full Sequential Reset

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 41

Loading...

Loading...