MC81F4204

April 24, 2012 Ver.1.41 81

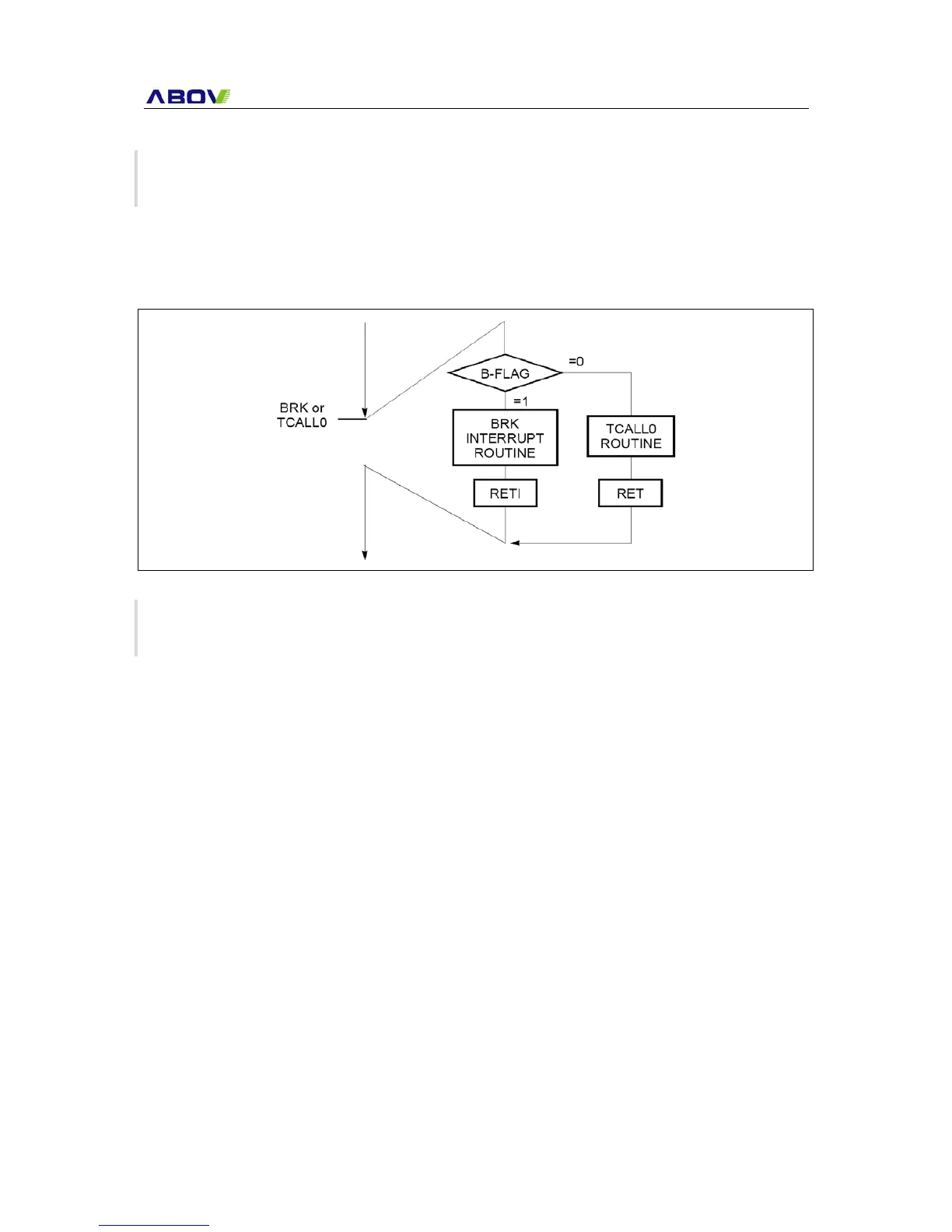

11.3 BRK Interrupt

Software interrupt can be invoked by BRK instruction, which has the lowest priority order. Interrupt

vector address of BRK is shared with the vector of TCALL 0 (Refer to Program Memory Section).

When BRK interrupt is generated, B-flag of PSW is set to distinguish BRK from TCALL 0.

Each processing step is determined by B-flag as shown in Figure

11.4 Shared Interrupt Vector

Some interrupts share the interrupt vector address. To recognize which interrupt is occurred, some

interrupt flag registers are used.

Note that, interrupt request bits are cleared after call the interrupt service routine. So interrupt request

bits can not be used to recognize which interrupt is occurred.

External Interrupt Group

In case of using interrupts of Ext group. It is necessary to check the EINTF register in the interrupt

service routine to find out which external interrupt is occurred. Because the 8 external interrupts share

the one interrupt vector address. These flag bits must be cleared by software after reading this

register.

Timer match / overflow

In case of using interrupts of Timer match and overflow together, it is necessary to check the INTFH

register in the interrupt service routine to find out which interrupt is occurred. Because the timer match

and overflow share the on interrupt vector address. See ‘

INTFH’ on page 78 to know which bit is

which.

Loading...

Loading...