MC81F4204

April 24, 2012 Ver.1.41 93

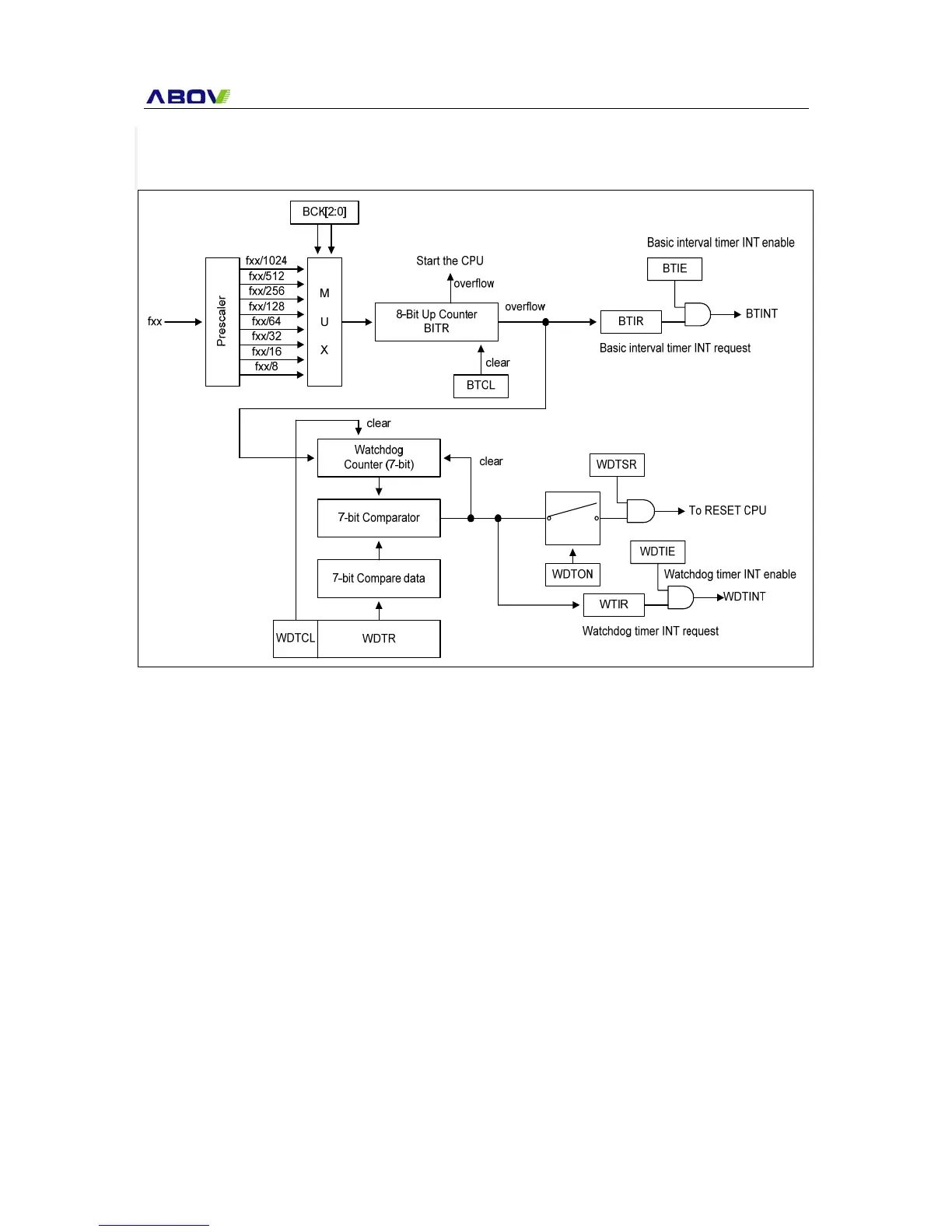

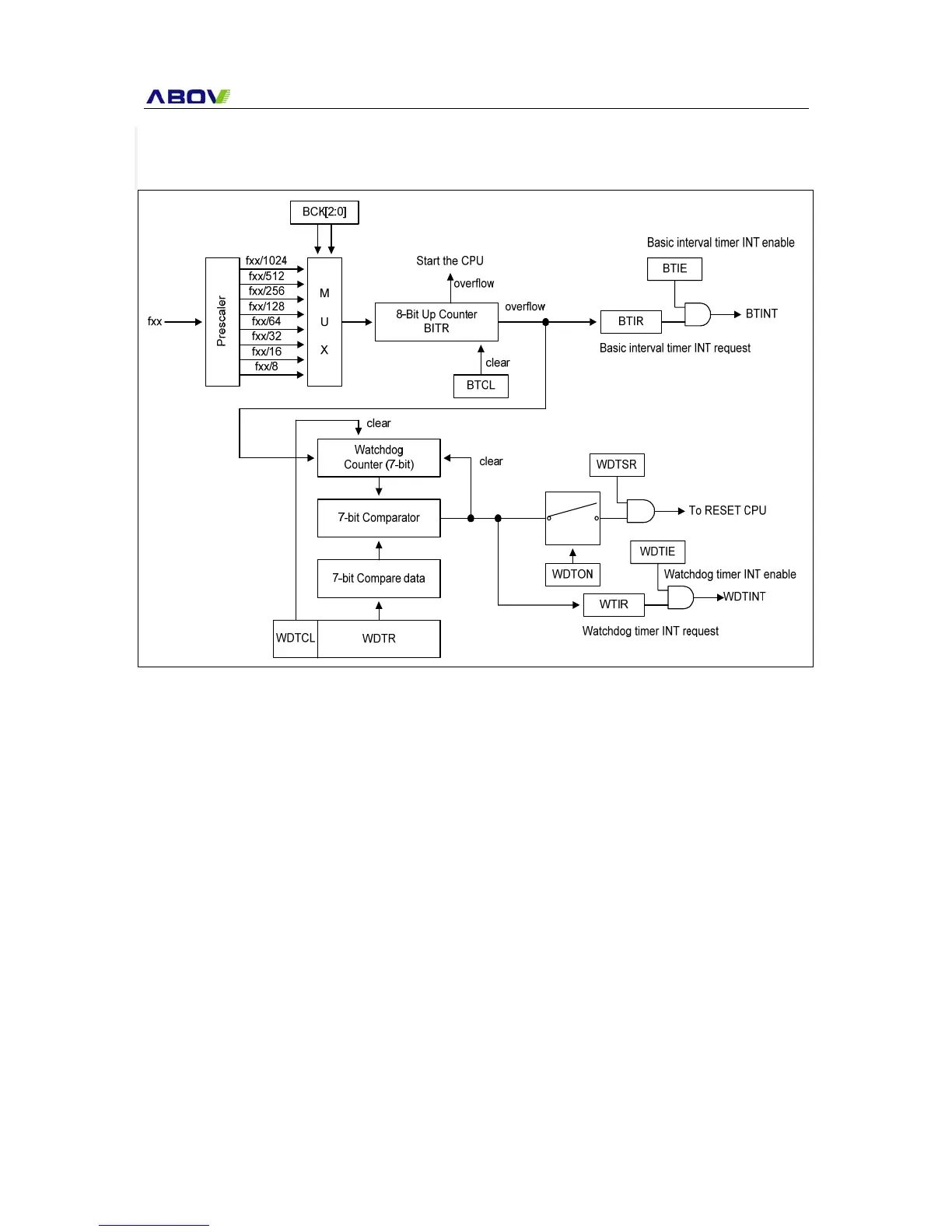

15. WATCH DOG TIMER

The watchdog timer rapidly detects the CPU malfunction such as endless looping caused by noise or

the like, and resumes the CPU to the normal state. The watchdog timer signal for detecting

malfunction can be selected either a reset CPU or a interrupt request.

When the watchdog timer is not being used for malfunction detection, it can be used as a timer to

generate an interrupt at fixed intervals.

The watchdog timer uses the Basic Interval Timer as a clock source.

The watchdog timer consists of 7-bit binary counter and the watchdog timer data register. When the

value of 7-bit binary counter is equal to the lower 7 bits of WDTR, the interrupt request flag is

generated. This can be used as Watchdog timer interrupt or reset the CPU in accordance with the bit

WDTON.

Watchdog reset feature is disabled when the watchdog timer status register(WDTSR) value is ‘0A5h’.

Note that, WDTSR’s reset value is ‘00h’. And reset value of WDTON is ‘1’. So watchdog timer reset is

enabled at reset time.

Figure 15-1 Block diagram of Basic Interval Timer/Watchdog Timer

Loading...

Loading...