MC81F4204

April 24, 2012 Ver.1.41 91

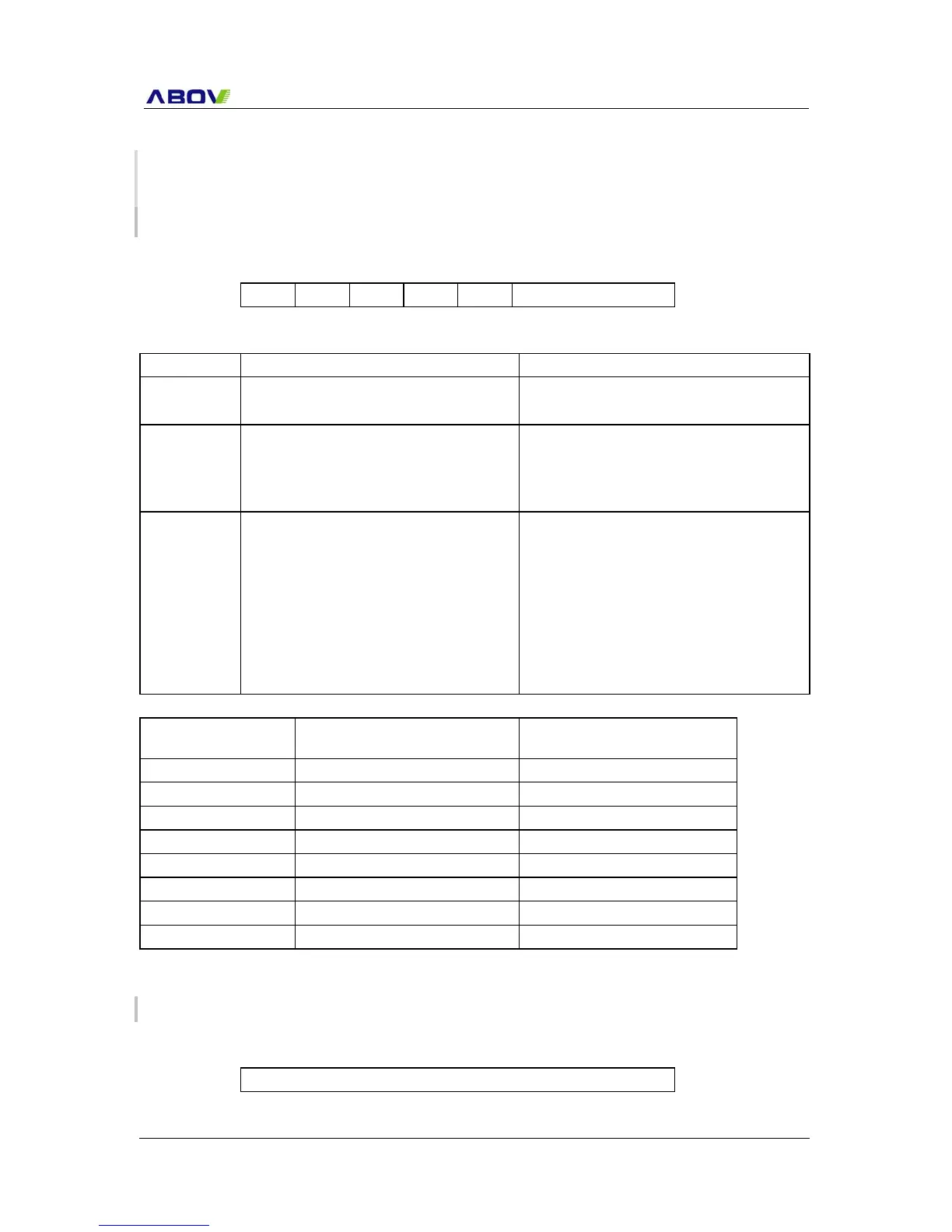

14.1 Registers

CKCTLR

CLOCK CONTROL REGISTER 00F2H

7 6 5 4 3 2 1 0

CKCTLR

– – – WDTON BTCL BTS

Reset value: 17H

– – – R/W R/W R/W R/W R/W

– bit7 – bit5 Not used for MC81F4204

0: Operate as 7-bit timer

WDTON

Watchdog Timer Enable Bit

1: Enable Watchdog timer

0: Normal operation (free-run)

BTCL

Basic Timer Clear Bit

1: Clear 8-bit counter (BITR) to “0”,

This bit becomes 0 automatically after one

machine cycle, and starts counting.

000: fxin/8

001: fxin/16

010: fxin/32

011: fxin/64

100: fxin/128

101: fxin/256

110: fxin/512

BTS

Basic Interval Timer Source Clock

Selection Bits

111: fxin/1024

CKCTLR[2:0] Source clock

Interrupt(overflow) period (ms)

@ fxin = 8MHz

000 fxin/8 0.256

001 fxin/16 0.512

010 fxin/32 1.024

011 fxin/64 2.048

100 fxin/128 4.096

101 fxin/256 8.192

110 fxin/512 16.384

111 fxin/1024 32.768

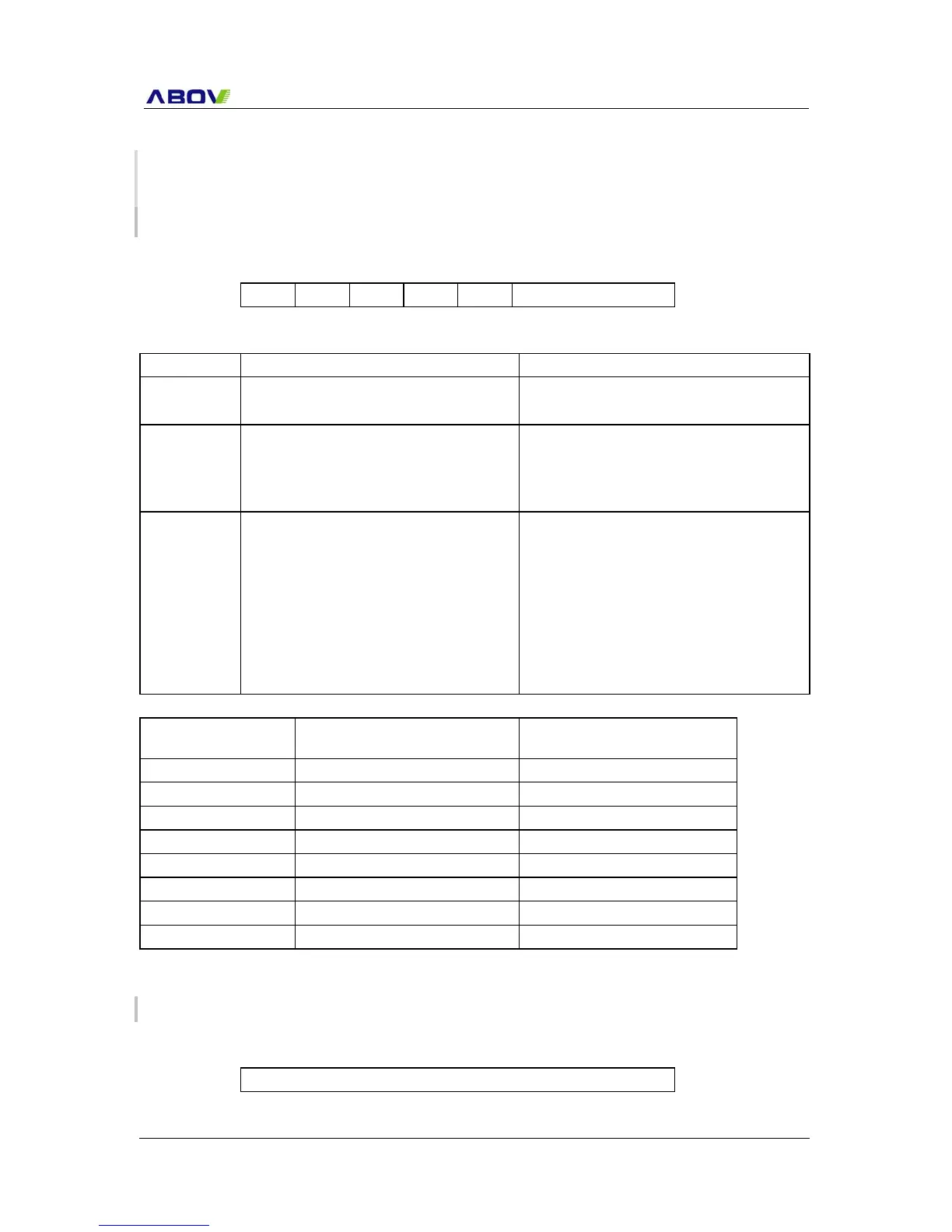

BTCR

BASIC TIMER COUNTER REGISTER 00F1H

7 6 5 4 3 2 1 0

BTCR

One byte register

Reset value: XXH

R R R R R R R R

Figure 14-1 Basic Interval Timer Interrupt Period

Loading...

Loading...