MC81F4204

94 April 24, 2012 Ver.1.41

15.1 Registers

WDTR

WATCHDOG TIMER REGISTER 00F4H

7 6 5 4 3 2 1 0

WDTR

WDTCL WDTCMP

Reset value: 7FH

R/W R/W R/W R/W R/W R/W R/W R/W

0: Free-run count

WDTCL

Watchdog Timer Clear Bit

1: When the WDTCL is set to “1”, binary

counter is cleared to “0”. And the WDTCL

becomes “0” automatically after one

machine cycle. Counter count up again.

WDTCMP

bit6 – bit0 7-bit compare data

WDTSR

WATCHDOG TIMER STATUS REGISTER 00F6H

7 6 5 4 3 2 1 0

WDTSR One byte register Reset value: 00H

R/W R/W R/W R/W R/W R/W R/W R/W

10100101: Disable watchdog timer function

Watchdog Timer Function Disable Code

(for System Reset)

Others: Enable watchdog timer function

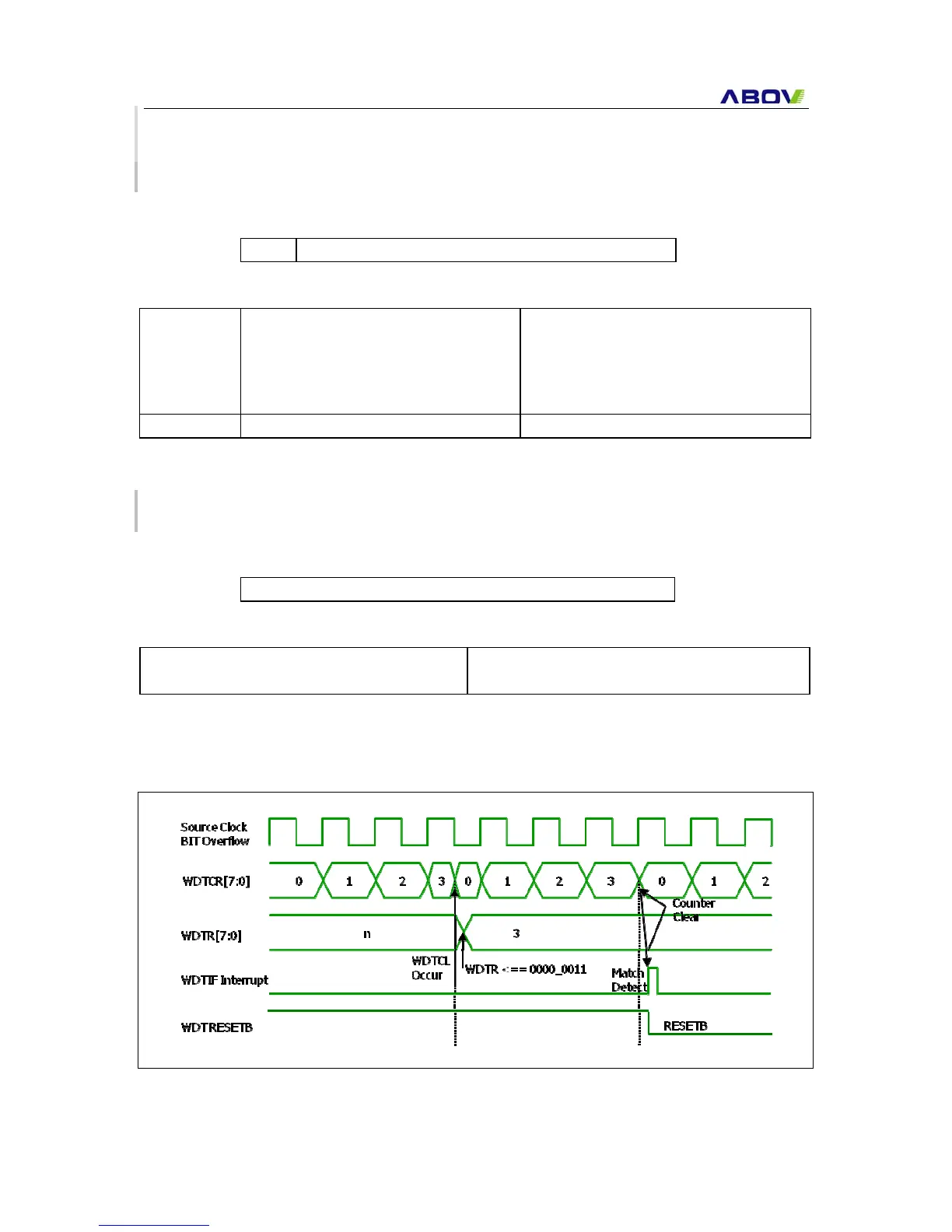

Figure 15-2 Watchdog Timer Timing

Loading...

Loading...