MC81F4204

82 April 24, 2012 Ver.1.41

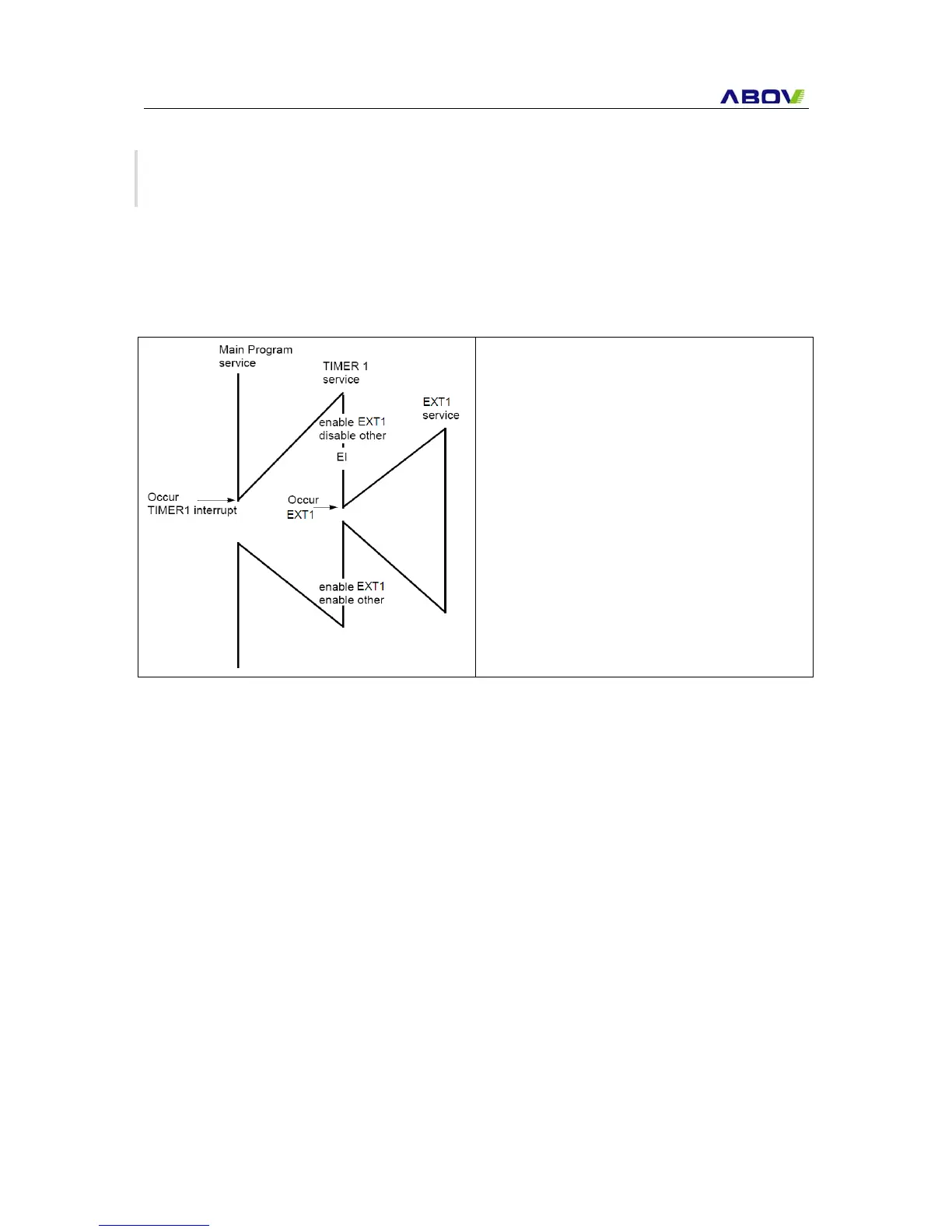

11.5 Multi Interrupt

If two requests of different priority levels are received simultaneously, the request of higher priority

level is serviced. If requests of the interrupt are received at the same time simultaneously, an internal

polling sequence determines by hardware which request is serviced. However, multiple processing

through software for special features is possible. Generally when an interrupt is accepted, the I-flag is

cleared to disable any further interrupt. But as user sets I-flag in interrupt routine, some further

interrupt can be serviced even if certain interrupt is in progress.

In this example, the EXT1 interrupt can be

serviced without any pending, even TIMER1 is in

progress.

Because of re-setting the interrupt enable

registers IENH,IENL and master enable “EI” in

the TIMER1 routine.

Figure 11-4 Execution of Multi Interrupt

Loading...

Loading...