SERIAL INTERFACE

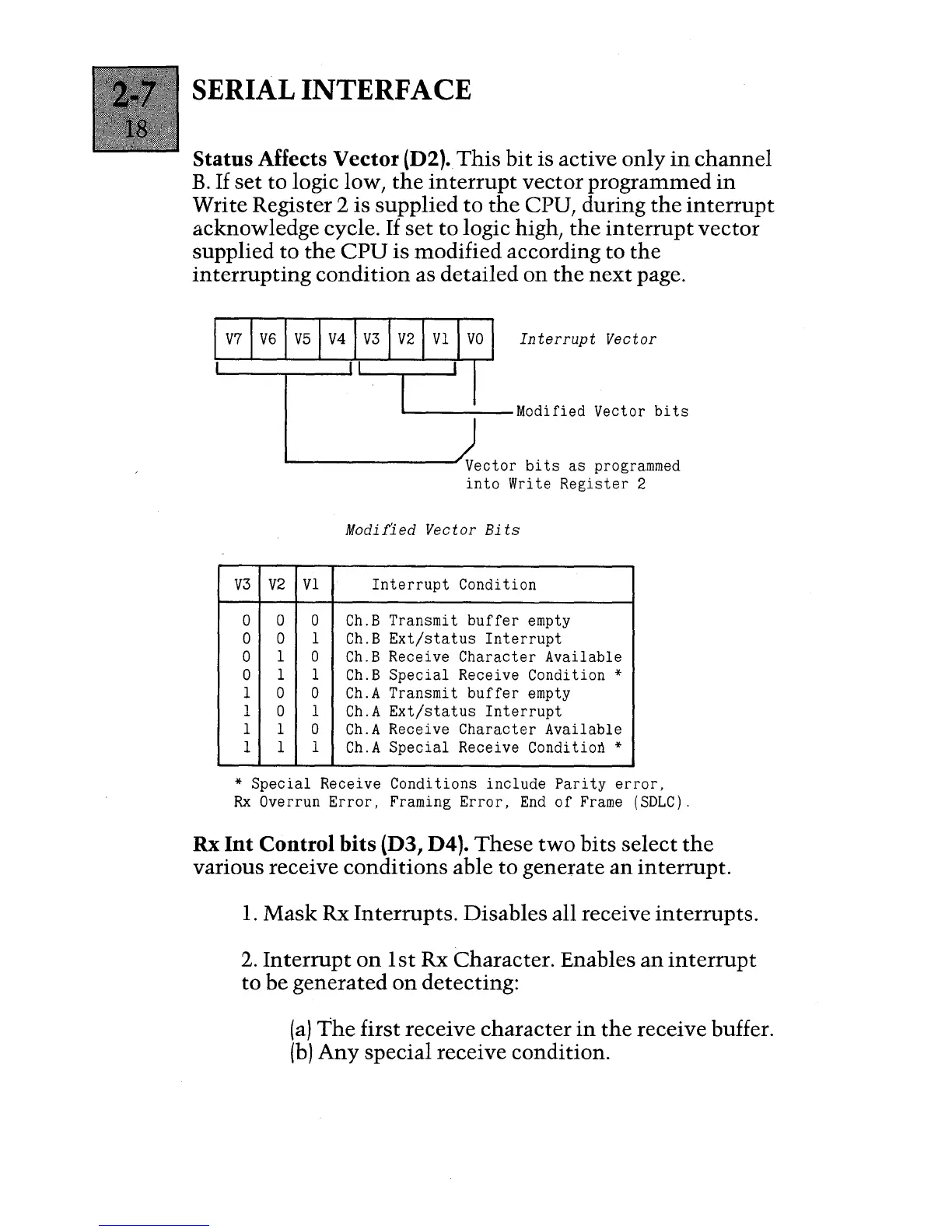

Status Affects Vector (D2}.This bit is active

only

in

channel

B.

If

set to logic low, the interrupt vector programmed

in

Write Register 2 is supplied to the CPU, during the interrupt

acknowledge cycle.

If

set

to

logic high, the interrupt vector

supplied to the

CPU

is

modified according to the

interrupting condition as detailed on the

next

page.

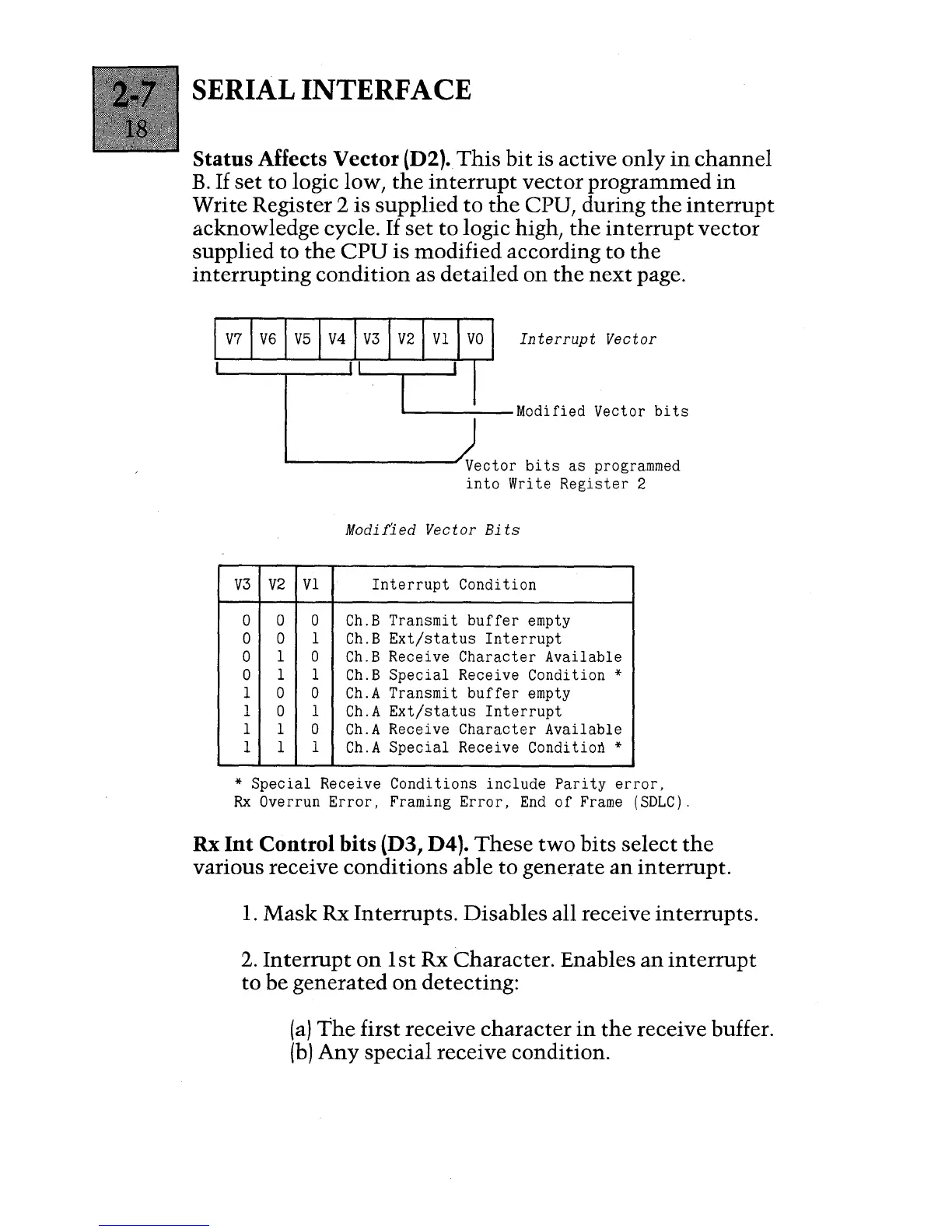

V3

0

0

0

0

1

1

1

1

Interrupt

Vector

L-

______

-JJ

Modi

fied

Vector

bits

- Vector

blts

as programmed

into

Write

Register

2

Modifled

Vector

Bits

V2

VI

Interrupt

Condition

0 0

Ch.B

Transmit

buffer

empty

0

I

Ch.B

Ext/status

Interrupt

1 0

Ch.B

Receive Character Available

1 I

Ch.B

Special

Receive Condition *

0 0

Ch.A

Transmit

buffer

empty

0

I

Ch.A

Ext/status

Interrupt

I 0

Ch.A

Receive

Character

Available

1

I

Ch.A

Special

Receive Condition *

*

Special

Receive Conditions

include

Parity

error,

Rx

Overrun

Error,

Framing

Error,

End

of

Frame

(SDLC).

Rx Int Control bits (D3, D4). These

two

bits select the

various receive conditions able to generate an interrupt.

1.

Mask Rx Interrupts. Disables all receive interrupts.

2. Interrupt

on

1st Rx Character. Enables an interrupt

to be generated

on

detecting:

(a)

the

first receive character

in

the receive buffer.

(b)

Any special receive condition.

Loading...

Loading...