ADAV4601 System Design Document Confidential Information

Rev.1 August 2009 Analog Devices Page 90

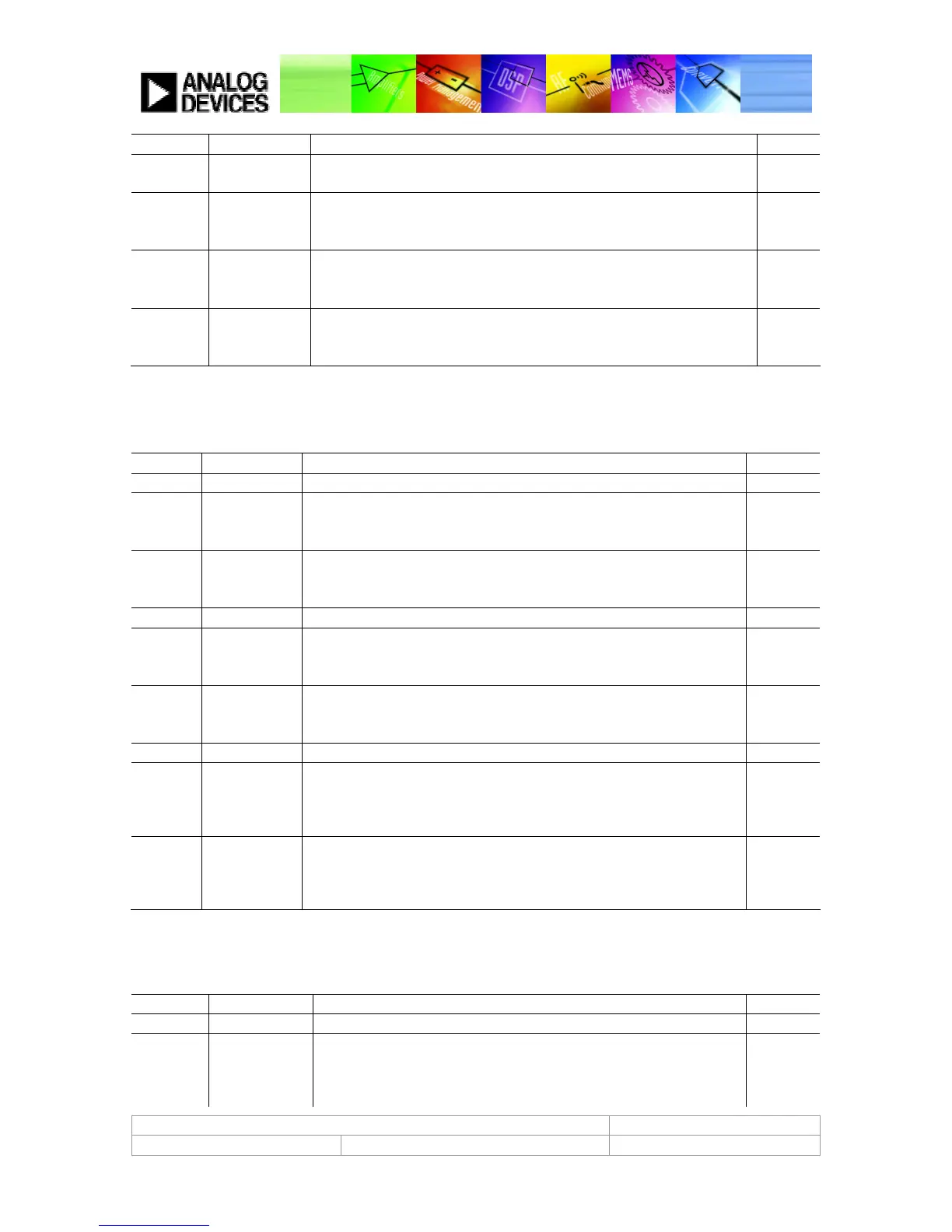

Bit No. Bit Name Description Default

1b = block powered up

0b = block powered down

Bit[2] HP1DAC left Powers on the HP1 DAC left channel. 0

1b = block powered up

0b = block powered down

Bit[1] HP1 AMP right Powers on the HP1 AMP right channel. 0

1b = block powered up

0b = block powered down

Bit[0] HP1 AMP left Powers on the HP1 AMP left channel. 0

1b = block powered up

0b = block powered down

Address 0x0007 Digital Power Management Register (Default: 0x0000)

Table 43.

Bit No. Bit Name Description Default

Bits[15:8] Reserved Always write as 0 if writing to this register. 00000000

Bit[7] PWM Powers on the PWM channels. 0

1b = block powered up

0b = block powered down

Bit[6] S/PDIF TX Powers on the S/PDIF transmitter. 0

1b = block powered up

0b = block powered down

Bit[5] Reserved Always write as 0 if writing to this register. 0

Bit[4] SRC2 Powers on SRC2. 0

1b = block powered up

0b = block powered down

Bit[3] SRC1 Powers on SRC1. 0

1b = block powered up

0b = block powered down

Bit[2] Reserved Always write as 0 if writing to this register. 0

Bit[1] ADC/DAC

engine

Powers on the ADC/DAC engine. 0

1b = block powered up

0b = block powered down

Bit[0] Audio

processor

Powers on the audio processor core. 0

1b = block powered up

0b = block powered down

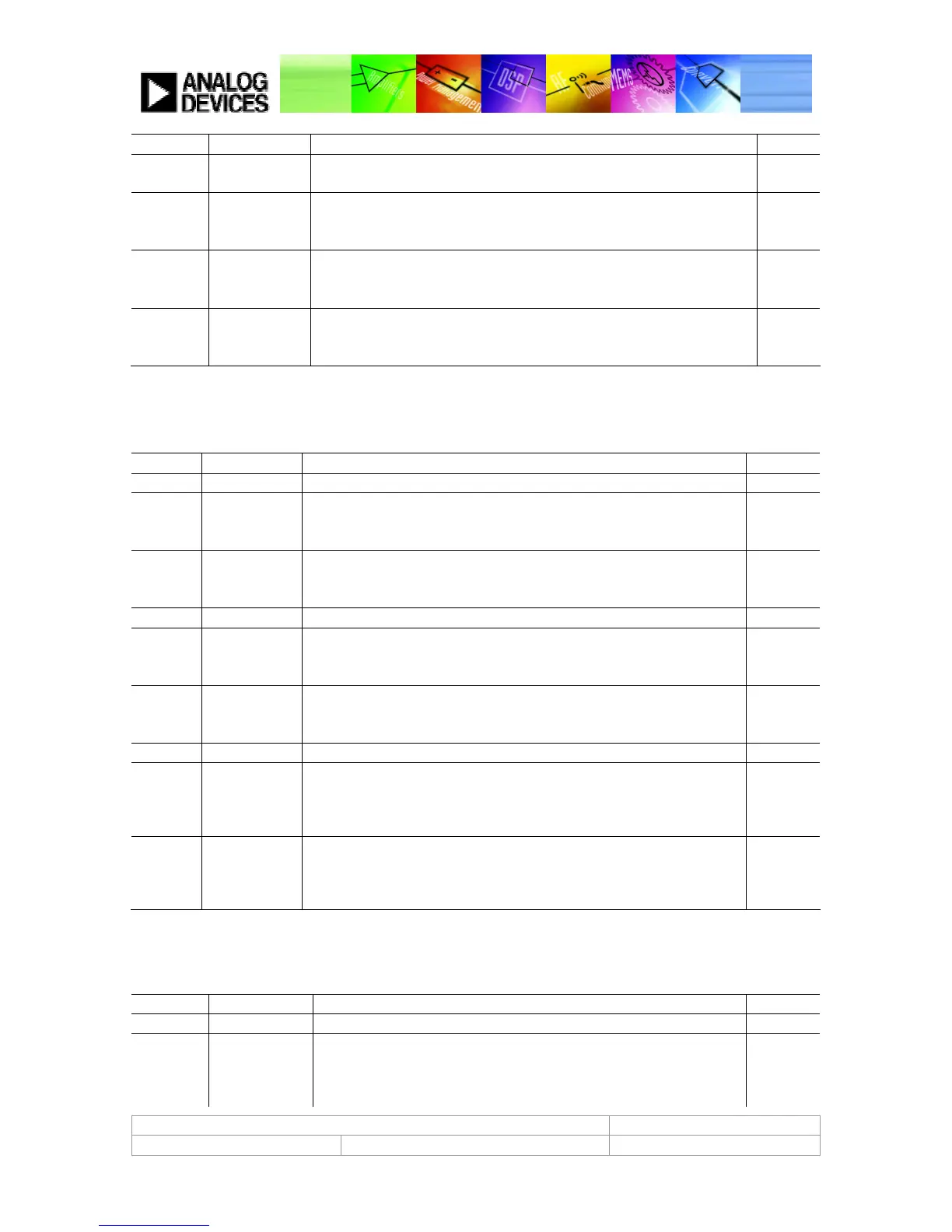

Address 0x0009 SPDIF Transmitter Control Register (Default: 0x0000)

Table 44.

Bit No. Bit Name Description Default

Bits[15:8] Reserved Always write as 0 if writing to this register. 00000000

Bits[14:12] SPDIF output

select

Selects the source for the SPDIF output. 000

000b = output internally generated SPDIF

001b = output SPDIF_IN2

Loading...

Loading...