ADAV4601 System Design Document Confidential Information

Rev.1 August 2009 Analog Devices Page 91

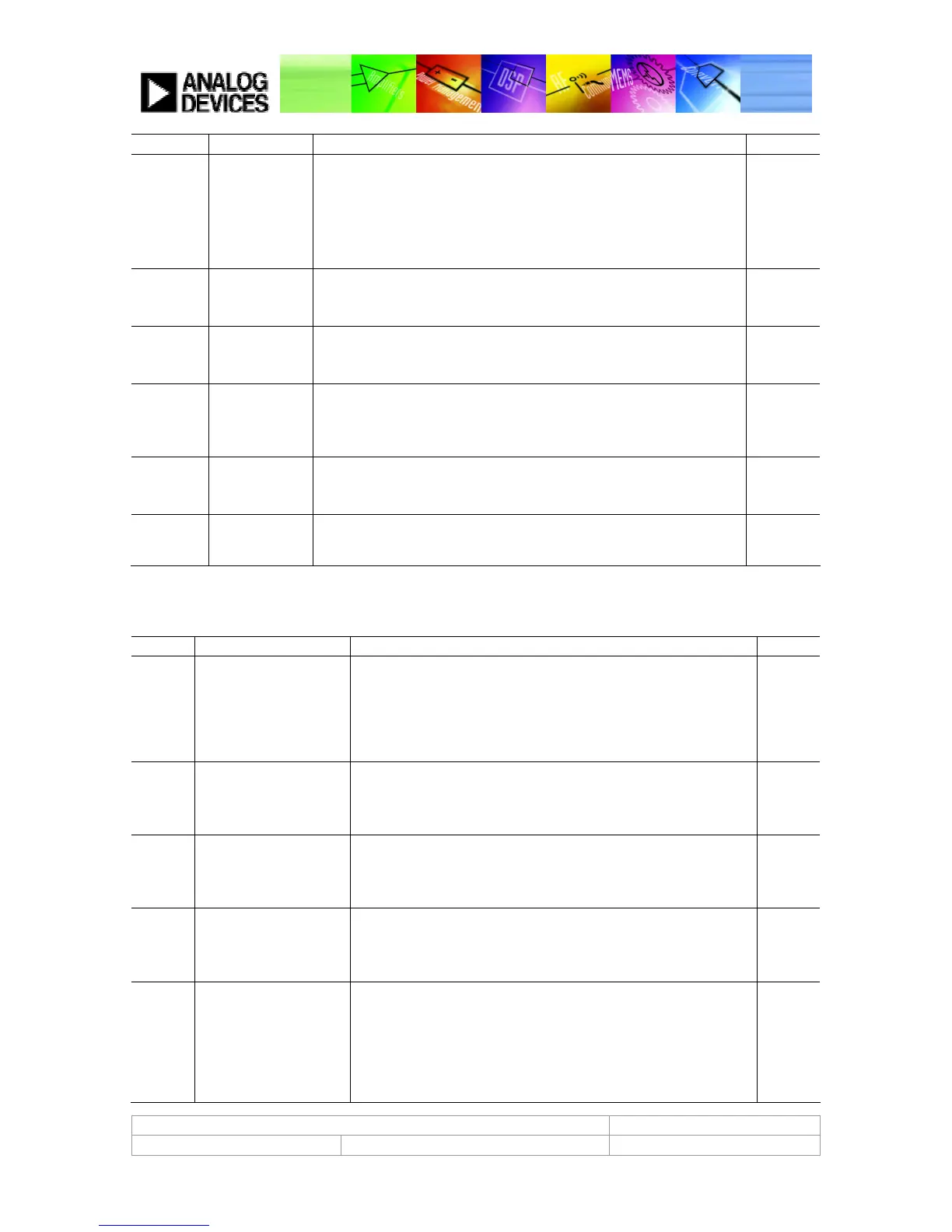

Bit No. Bit Name Description Default

010b = output SPDIF_IN1

011b = output SPDIF_IN0

100b = output SPDIF_IN3

101b = output SPDIF_IN4

110b = output SPDIF_IN5

111b = output SPDIF_IN6

Bit[11] SPDIF disable Enable or disables the SPDIF transmitter. 0

0b = enabled

1b = disabled

Bit[10] PRE Edge Sets the edge to be used for the preamble. 0

0b = rising edge

1b = falling edge

Bit[9] Validity

polarity

Used to indicate to the receiver if the data in the transmitted stream is

valid audio data.

0

0b = valid data sent

1b = invalid data sent

Bit[8] Copy flag Used to indicate to the receiver if the data is copyright material. 0

0b = copyright

1b = not copyright

Bits[7:0] Channel status Used to specify the type of equipment in use. Not applicable when the

SPDIF Mux Bits[14:12]

are set to anything other than 000b.

00000000

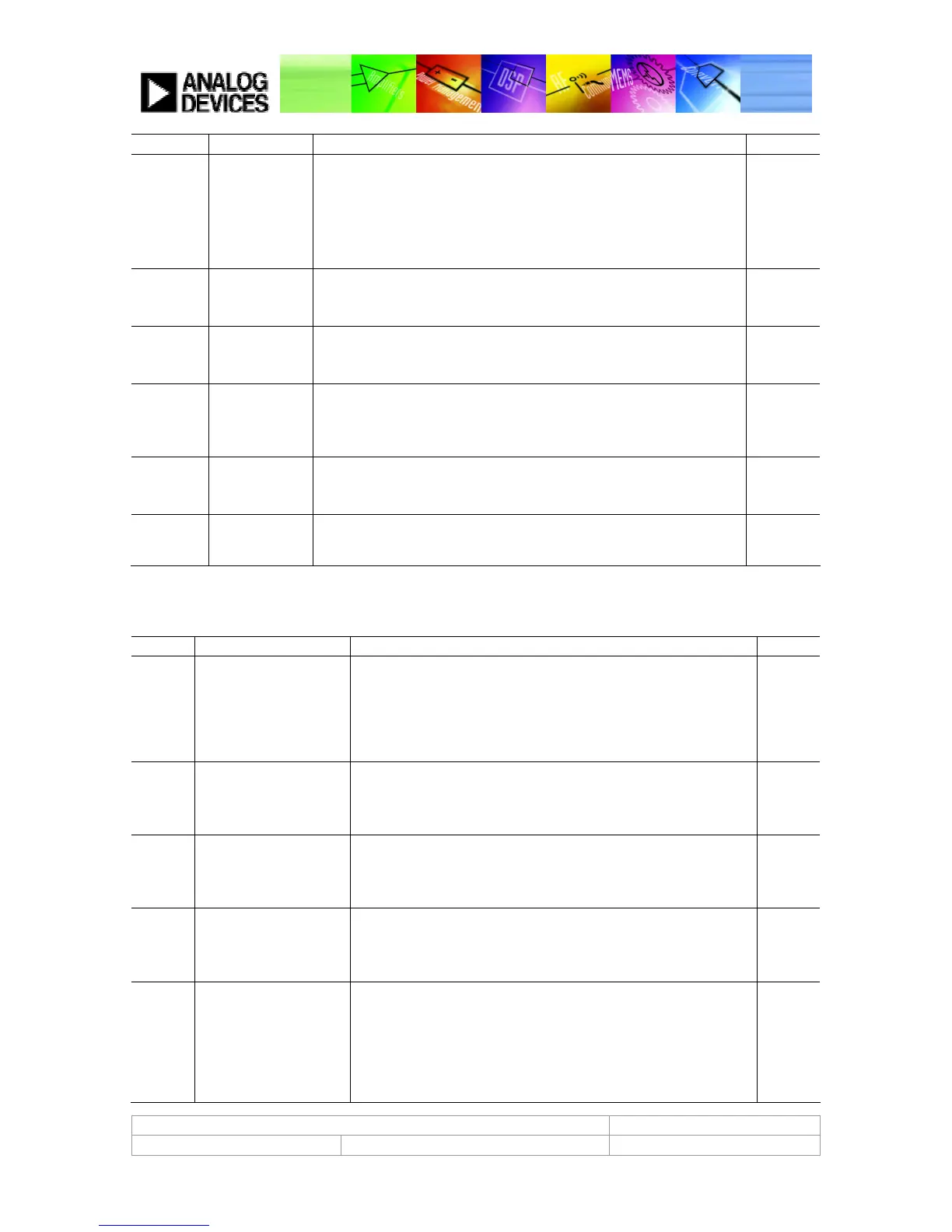

Address 0x000A Misc Control Register (Default: 0x8000)

Table 45.

Bit No. Bit Name Description Default

Bit[15] PWM ready flag (read-

only)

Indicates the current status of the PWM ready pin. When PWM

ready is low, the

PWM is not enabled. When PWM ready is high, the PWM is enabled

and stable.

0

0b = PWM ready pin low

1b = PWM ready pin high

Bit[14] Enable selected PWM

channels

When enabled, all PWM channels selected by Bits[10:7] can be

used.

0

0b = all PWM channels disabled

1b = selected PWM channels enabled

Bit[13] MCLK_OUT CLK type

select

Used to configure the MCLK_OUT pin. 0

0b = crystal frequency on MCLK_OUT

1b = internally generated clocks on MCLK_OUT

Bit[12] PWM enable/disable

patterns

Enables the enable/disable patterns for the PWM block. 0

0b = enable/disable pattern not used

1b = Use enable/disable pattern

Bit[11] DAC mod offset Adds dc offset to the DAC Σ-∆ modulator to eliminate idle tones. It is

recommended

that this bit is disabled before the ADC/DAC engine is powered up

in

Control Register 0x0007[1].

1

0b = enabled

1b = disabled

Loading...

Loading...