ADAV4601 System Design Document Confidential Information

Rev.1 August 2009 Analog Devices Page 93

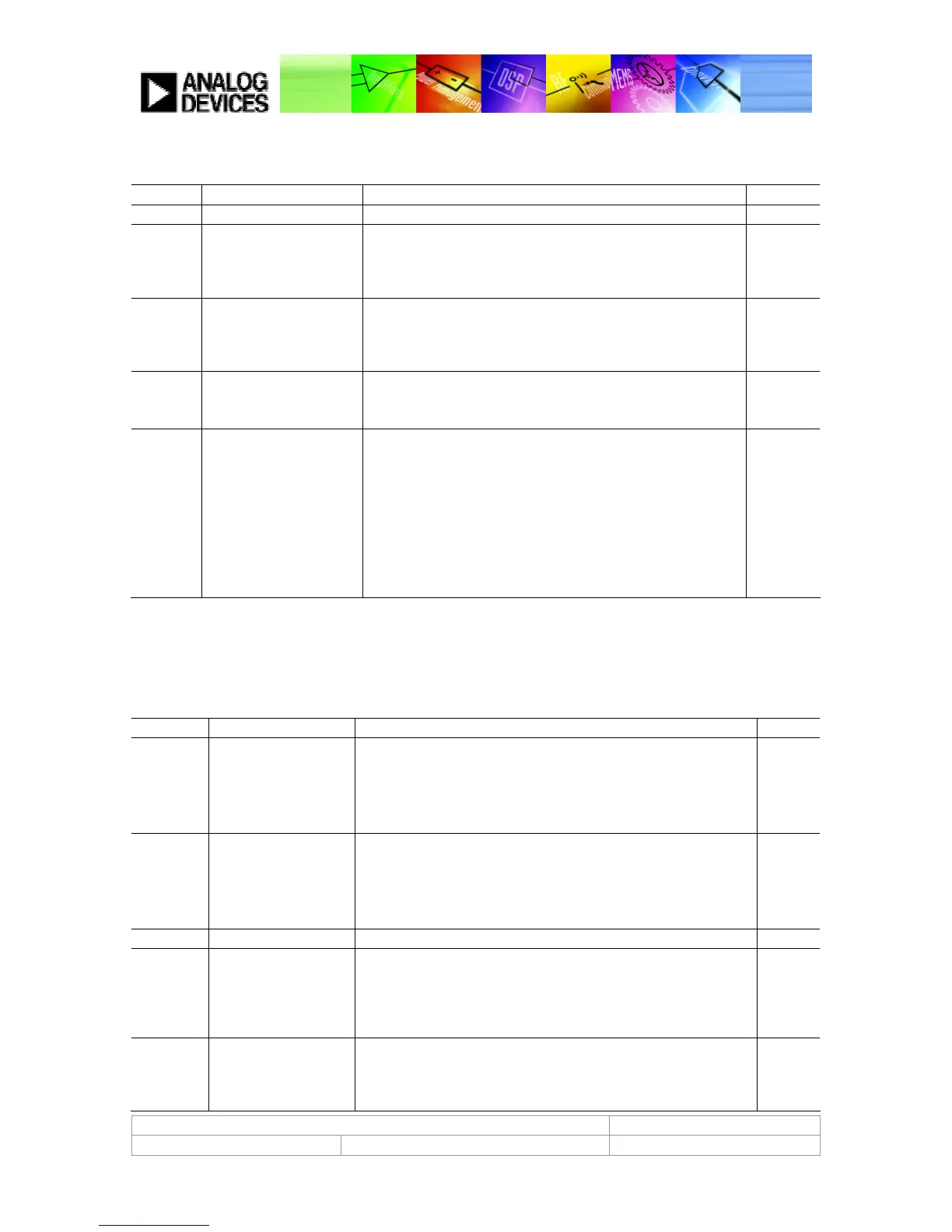

Address 0x000B Headphone Control Register (Default: 0x0000)

Table 46.

Bit No. Bit Name Description Default

Bits[15:8] Reserved Always write as 0 if writing to this register. 00000000

Bit[7] HP1 mute When set to 1, mutes the headphone output immediately

without ramping.

0

0b = unmuted

1b = mute

Bit[6] HP1 short-circuit protect Enable the short-circuit protection for the headphone

amplifier.

0

0b = disabled

1b = enabled

Bit[5] HP1 tristate Disables tristating of the headphone amplifier. 0

0b = enabled

1b = disabled

Bits[4:0] Headphone 1

gain/attenuation

Used to apply analog attenuation to the headphone amplifier. 00000

00000b = 0 dB

00001b = −1.5 dB

00010b = −3 dB

…

11101b = −43.5 dB

11110b = −45 dB

11111b = +1.5 dB

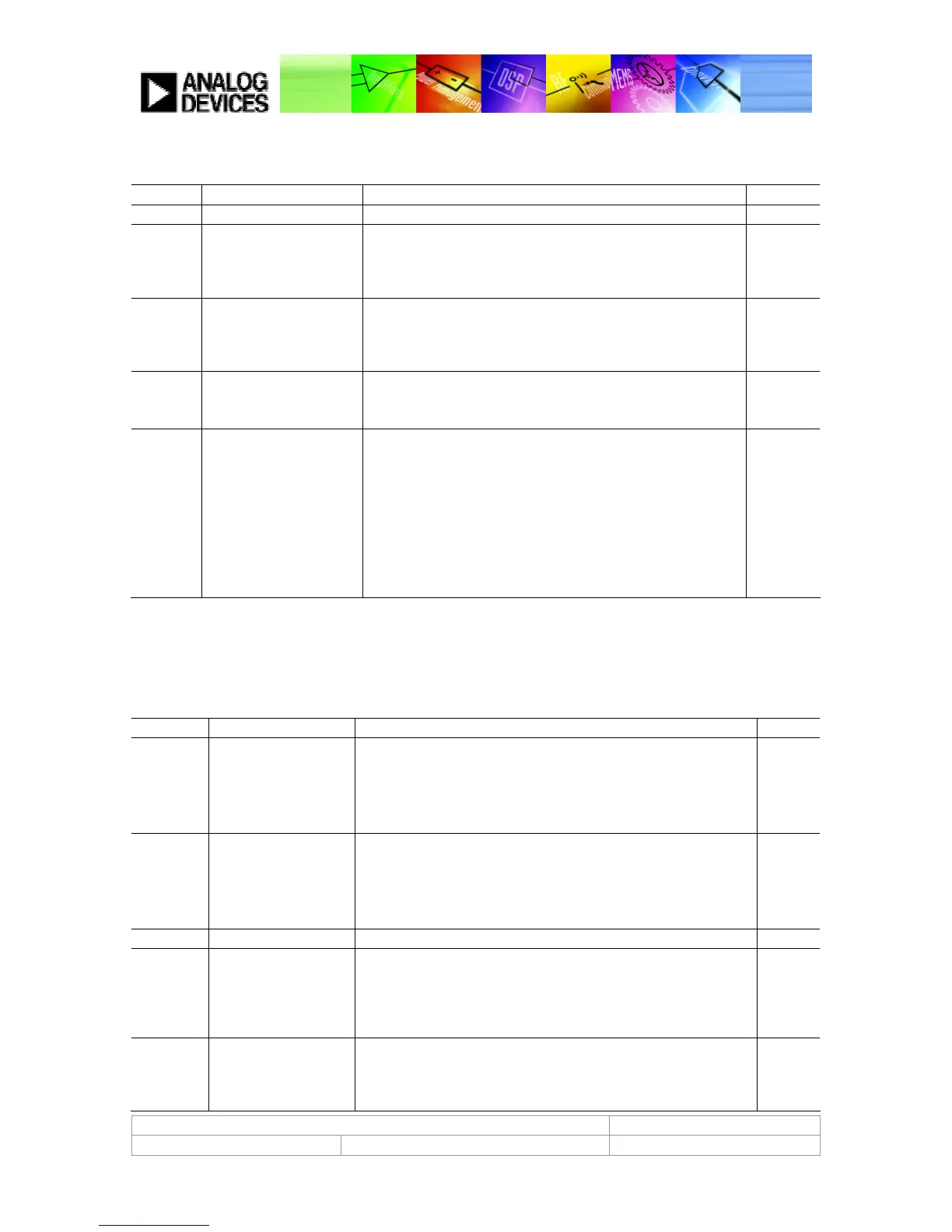

Address 0x000C Serial Port Control 2 Register (Default: 0x8004)

It should be noted that the SDIN3, LRCLK0, BCLK0, LRCLK1, BCLK1, LRCLK2, and BCLK2 can also be used as

SPDIF_IN0, SPDIF_IN1, SPDIF_IN2, SPDIF_IN3, SPDIF_IN4, SPDIF_IN5, and SPDIF_IN6.

Table 47.

Bit No. Bit Name Description Default

Bits[15:14] SCR2 clock select Used to select the serial clocks used for the input to SRC2. 10

00b = uses LRCLK0 and BCLK0

01b = uses LRCLK1 and BCLK1

10b = uses LRCLK2 and BCLK2

11b = Reserved

Bits[13:12] SRC1 clock select Used to select the serial clocks used for the input to SRC1. 00

00b = uses LRCLK0 and BCLK0

01b = uses LRCLK1 and BCLK1

10b = uses LRCLK2 and BCLK2

11b = Reserved

Bit[11] Reserved Always write as 0 if writing to this register. 0

Bit[10] Digout Enable 1 Used to change the function of the PWM1A and PWM1B pins to

additional serial

digital outputs, SDO2 and SDO3.

0

0b = PWM1A and PWM1B in normal operation

1b = PWM1A and PWM1B used as SDO2 and SDO3

Bit[9] Digout Enable 2 Used to change the function of SPDIF output to serial digital

output SDO1.

0

0b = SPDIF output normal operation

1b = SPDIF output used as SDO1

Loading...

Loading...