ADAV4601 System Design Document Confidential Information

Rev.1 August 2009 Analog Devices Page 92

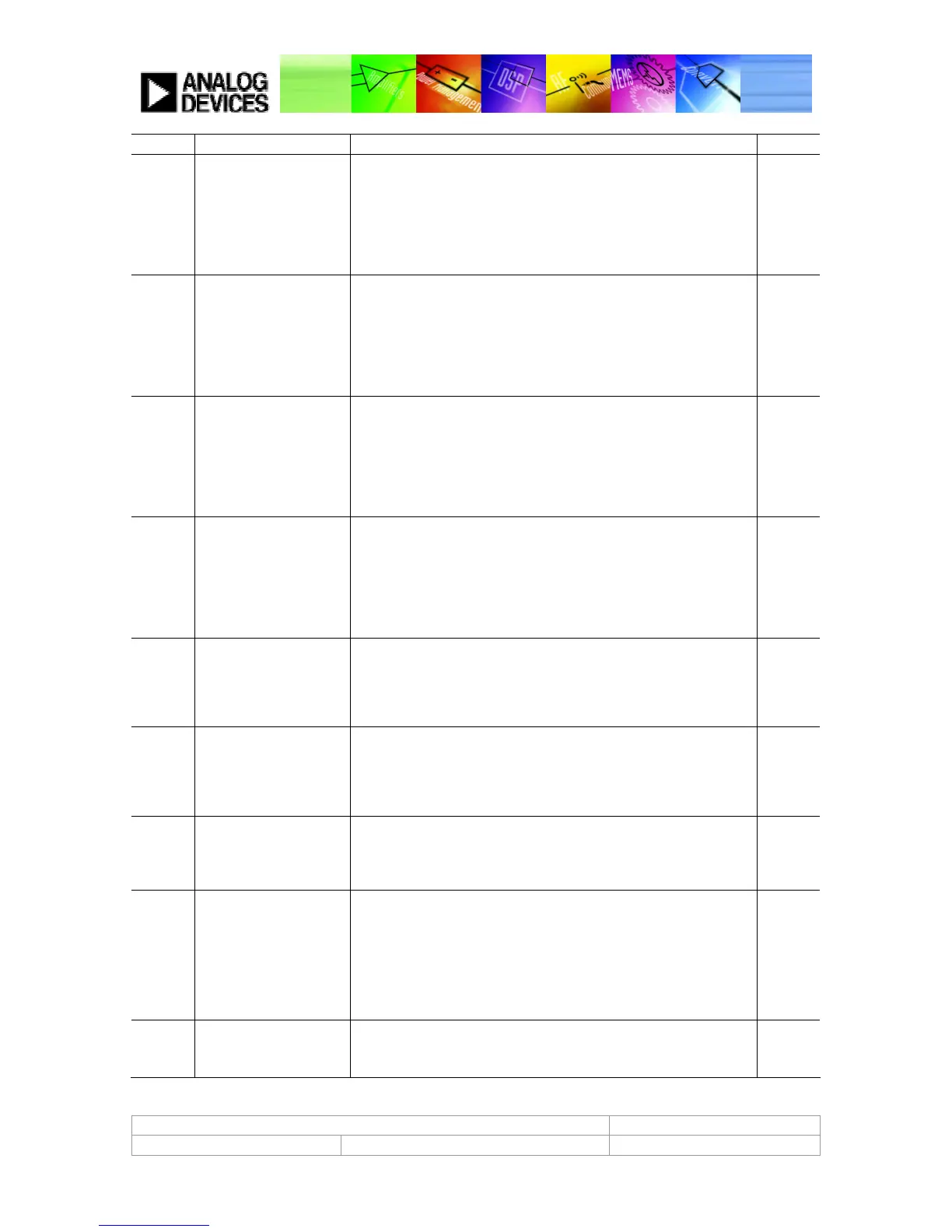

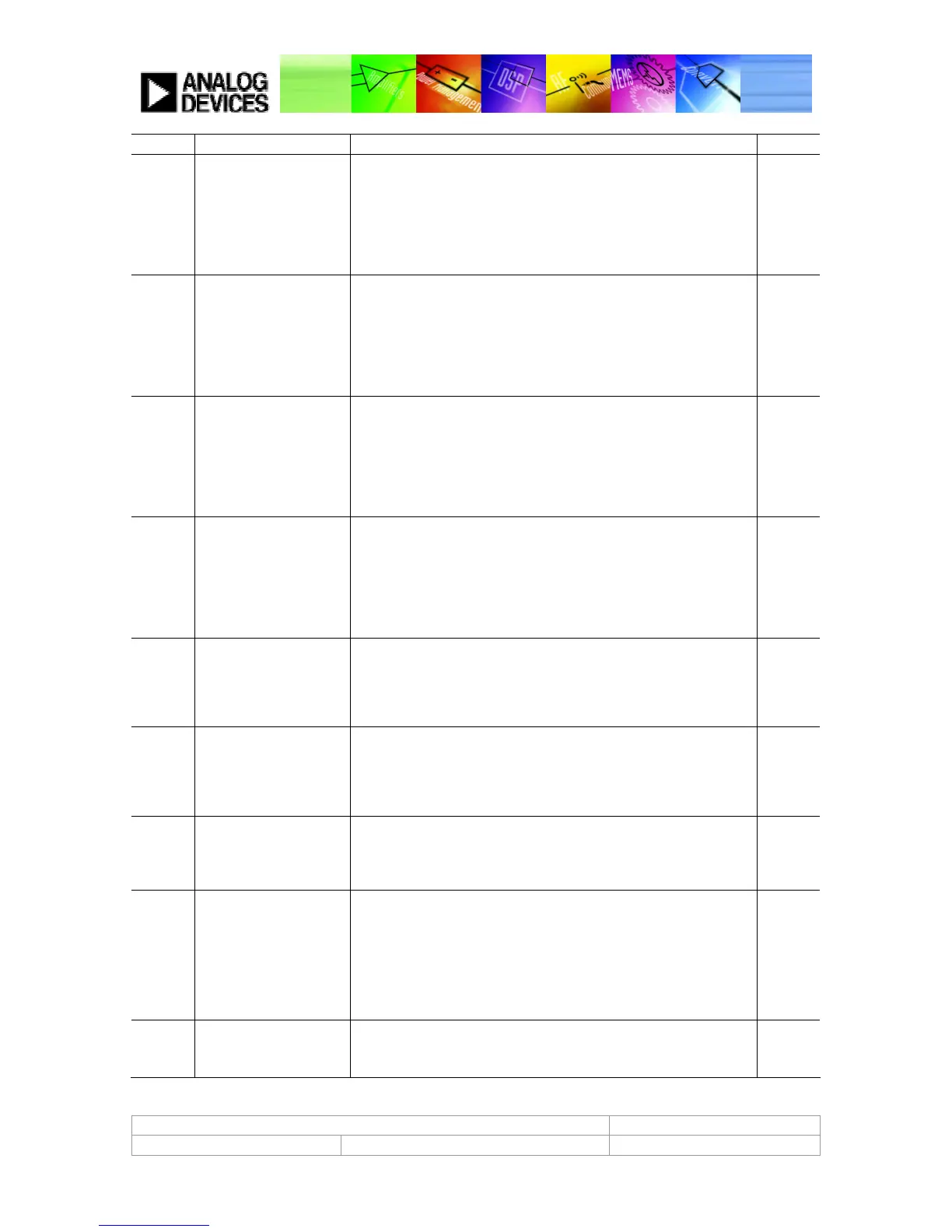

Bit No. Bit Name Description Default

Bit[10] PWM Enable 4 The PWM outputs are disabled by default, which means that the

outputs are

at GND. When this bit is set to 1 and Bit[14] of this register is set to

1, then the

PWM Enable 4 channel is enabled.

0

0b = disabled

1b = enabled

Bit[9] PWM Enable 3 The PWM outputs are disabled by default, which means that the

outputs are

at GND. When this bit is set to 1 and Bit[14] of this register is set to

1, then the

PWM Enable 3 channel is enabled.

0

0b = disabled

1b = enabled

Bit[8] PWM Enable 2 The PWM outputs are disabled by default, which means that the

outputs are

at GND. When this bit is set to 1 and Bit[14] of this register is set to

1, then the

PWM Enable 2 channel is enabled.

0

0b = disabled

1b = enabled

Bit[7] PWM Enable 1 The PWM outputs are disabled by default, which means that the

outputs are

at GND. When this bit is set to 1 and Bit[14] of this register is set to

1, then the

PWM Enable 1 channel is enabled.

0

0b = disabled

1b = enabled

Bit[6] SRC2 lock (read-only) Set to 1 when the sample rate converter (SRC) locks to the

incoming data,

indicating the data is valid.

0

0b = not locked

1b = locked

Bit[5] SRC1 lock (read-only) Set to 1 when the sample rate converter (SRC) locks to the

incoming data,

indicating the data is valid.

0

0b = not locked

1b = locked

Bit[4] MCLK_OUT Enable Enables the clock chosen by Bit[13] and Bits[3:1] to be output on

the MCLK_OUT pin.

0

0b = MCLK_OUT function disabled

1b = MCLK_OUT function enabled

Bits[3:1] Select internally

generated clock

Selects the frequency of the internally generated clock to be output on

the MCLK_OUT pin.

000

000b = crystal clock from internal PLL

001b = audio processor clock (122.88 MHz/2560 × FS)

010b = engine clock 49.152 MHz/1024 × FS)

011b = SRC clock/2 (24.576 MHz/512 × FS)

1xxb = modulator clock (6.144 MHz/128 × FS)

Bit[0] PLL enable Enables the PLL. 0

0b = PLL bypassed

1b = PLL enabled

Loading...

Loading...