ADAV4601 System Design Document Confidential Information

Rev.1 August 2009 Analog Devices Page 97

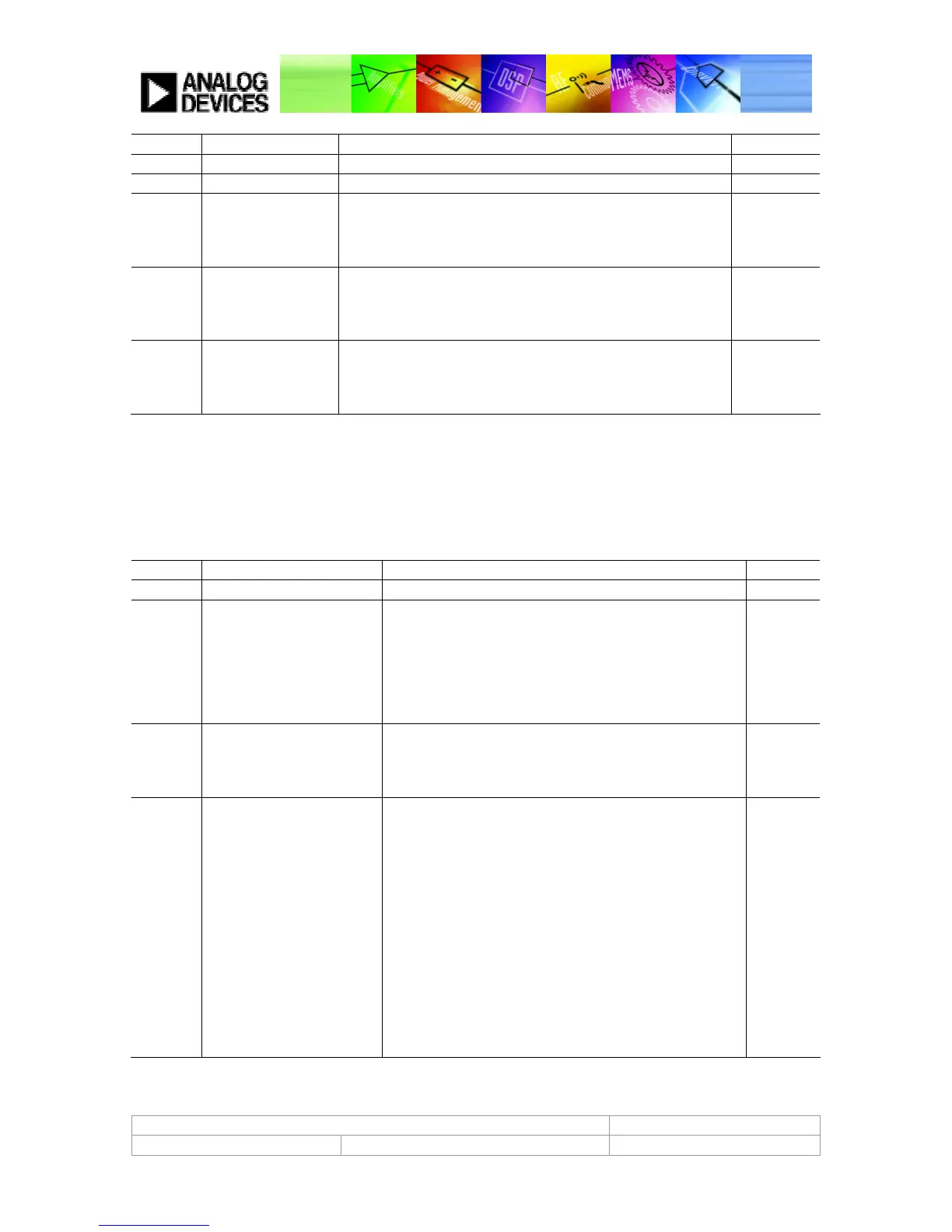

Bit No. Bit Name Description Default

1b = Amplifer in low power mode

Bits[3] Reserved Always write as 0 if writing to this register. 0

Bit[2] AUXDAC1 Standby Set to 0 after reset, which means the DAC is in normal mode but

is still powered down.

0

0b = DAC in normal mode

1b = DAC in low power mode

Bit[1] AUXDAC3 Standby Set to 0 after reset, which means the DAC is in normal mode but

is still powered down.

0

0b = DAC in normal mode

1b = DAC in low power mode

Bits[0] HP1 DAC Standby Set to 0 after reset, which means the HP DAC is in normal mode

but is still powered down.

0

0b = DAC in normal mode

1b = DAC in low power mode

Address 0x008D Reserved (Default: 0x0220)

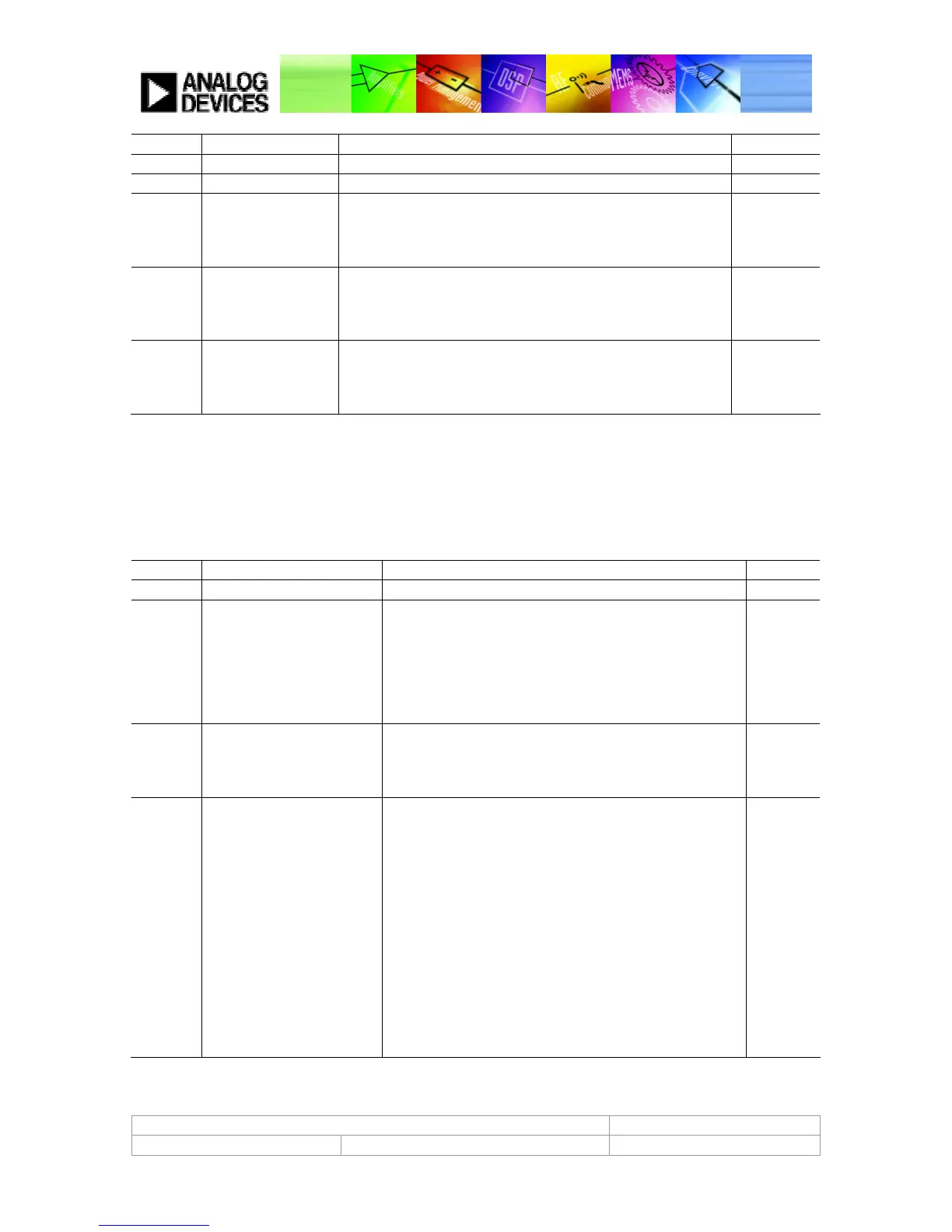

Address 0x008E SPDIF Transmitter Control 2 Register (Default: 0x002D)

Table 53.

Bit No. Bit Name Description Default

Bits[15:8] Reserved Always write as 0 if writing to this register. 00000000

Bits[7:4] Channel status sampling

frequency

Used to set the channel status sampling rate in the SPDIF

transmitted

stream. Should not change the sample rate but only the

status bits.

0010

0x0 = 44.1 kHz

0x2 = 48 kHz

0x3 = 32 kHz

Bit[3] SPDIF TX word length field

size

Selects the maximum SPDIF transmitter word length. 1

0b = 20 bits maximum

1b = 24 bits maximum

Bits[2:0] Transmitter word length Used to select how many of the bits set by Bit[3] carry valid

data.

If 24-bit maximum:

101

0x5 = 24 bits

0x4 = 23 bits

0x2 = 22 bits

0x6 = 21 bits

0x1 = 20 bits

If 20-bit maximum:

0x5 = 20 bits

0x4 = 19 bits

0x2 = 18 bits

0x6 = 17 bits

0x1 = 16 bits

Loading...

Loading...