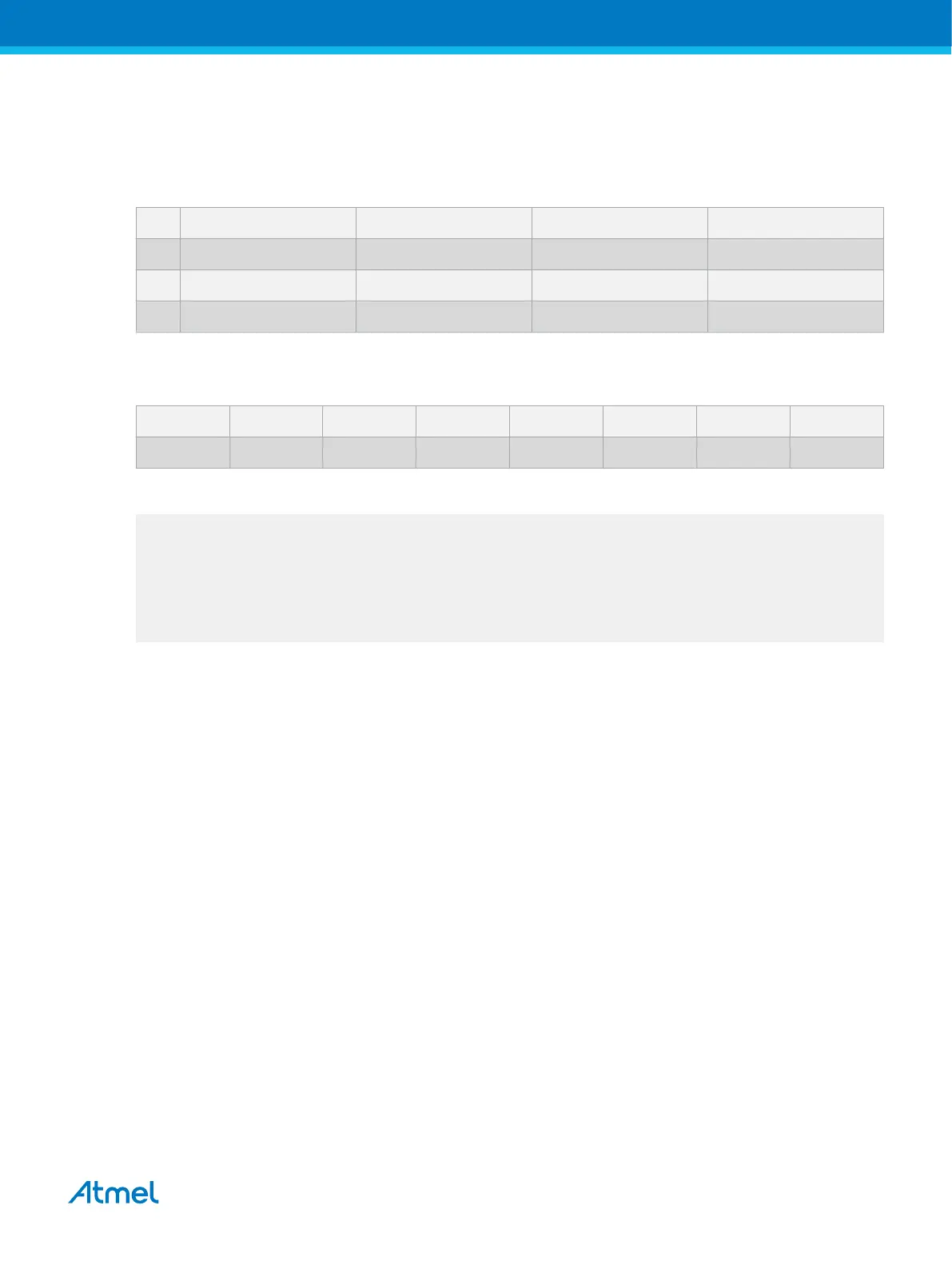

(iii) LD Rd, -Y 0 ≤ d ≤ 31 PC ← PC + 1

(iv) LDD Rd, Y+q 0 ≤ d ≤ 31, 0 ≤ q ≤ 63 PC ← PC + 1

16-bit Opcode:

(i) 1000 000d dddd 1000

(ii) 1001 000d dddd 1001

(iii) 1001 000d dddd 1010

(iv) 10q0 qq0d dddd 1qqq

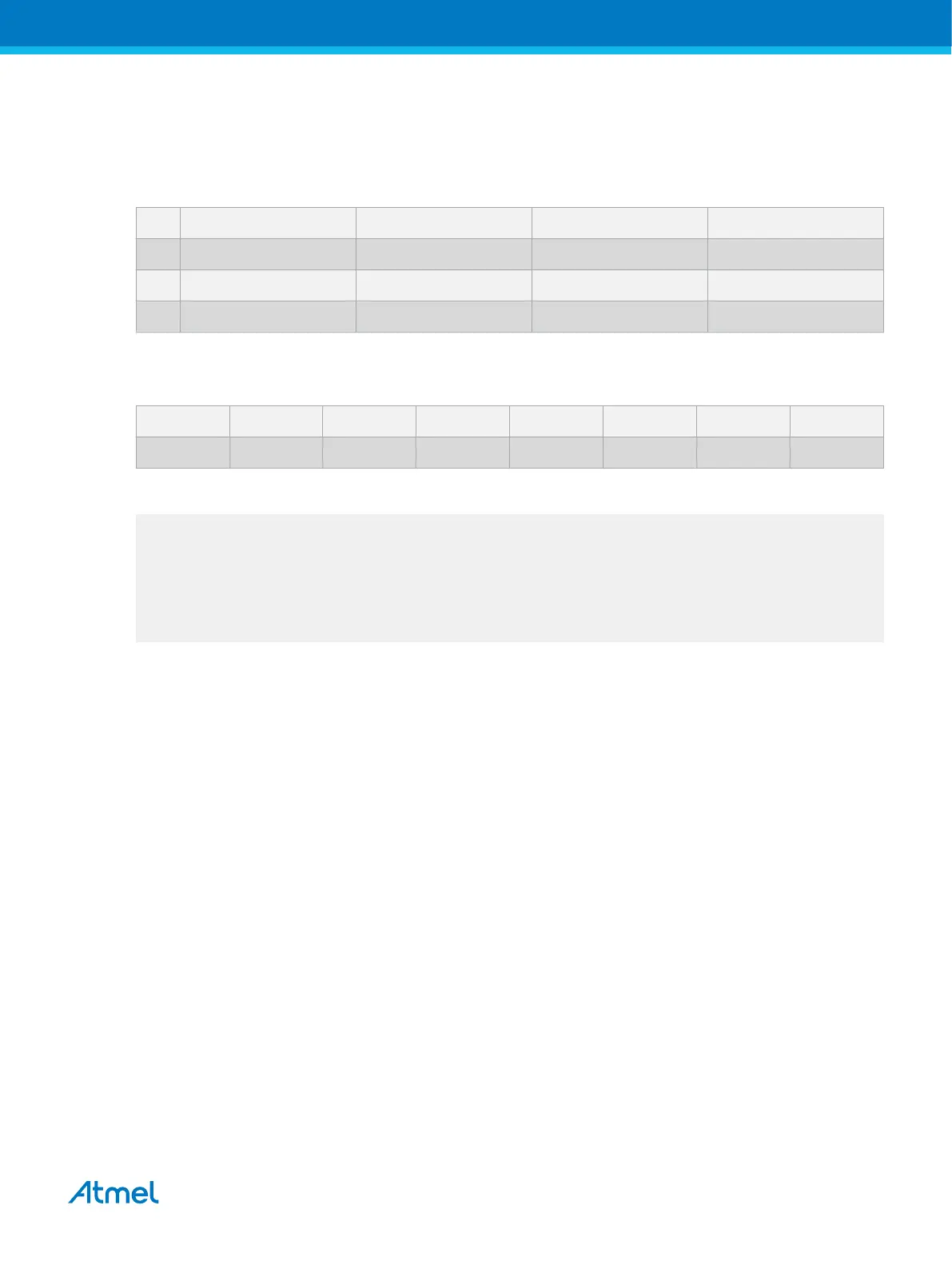

71.2. Status Register (SREG) and Boolean Formula

I T H S V N Z C

– – – – – – – –

Example:

clr r29 ; Clear Y high byte

ldi r28,$60 ; Set Y low byte to $60

ld r0,Y+ ; Load r0 with data space loc. $60(Y post inc)

ld r1,Y ; Load r1 with data space loc. $61

ldi r28,$63 ; Set Y low byte to $63

ld r2,Y ; Load r2 with data space loc. $63

ld r3,-Y ; Load r3 with data space loc. $62(Y pre dec)

ldd r4,Y+2 ; Load r4 with data space loc. $64

Words 1 (2 bytes)

Cycles (i): 1

(2)

(ii): 2

(iii): 3

(2)

Cycles XMEGA (i): 1

(1)

(ii): 1

(1)

(iii): 2

(1)

(iv): 2

(1)

1. Note: If the LD instruction is accessing internal SRAM, one extra cycle is inserted.

2. Note: LD instruction can load data from program memory since the flash is memory mapped.

Loading data from the data memory takes one clock cycle, and loading from the program memory

takes two clock cycles. But if an interrupt occur (before the last clock cycle) no additional clock

cycles are necessary when loading from the program memory. Hence, the instruction takes only

one clock cycle to execute.

LD instruction with pre-decrement can load data from program memory since the flash is memory

mapped. Loading data from the data memory takes two clock cycles, and loading from the program

memory takes three clock cycles. But if an interrupt occur (before the last clock cycle) no additional

Atmel AVR Instruction Set Manual [OTHER]

Atmel-0856L-AVR-Instruction-Set-Manual_Other-11/2016

110

Loading...

Loading...