78. LSR – Logical Shift Right

78.1. Description

Shifts all bits in Rd one place to the right. Bit 7 is cleared. Bit 0 is loaded into the C Flag of the SREG.

This operation effectively divides an unsigned value by two. The C Flag can be used to round the result.

Operation:

(i)

→

0

→

b7 - - - - - - - - - - - - - - - - - - b0

→

C

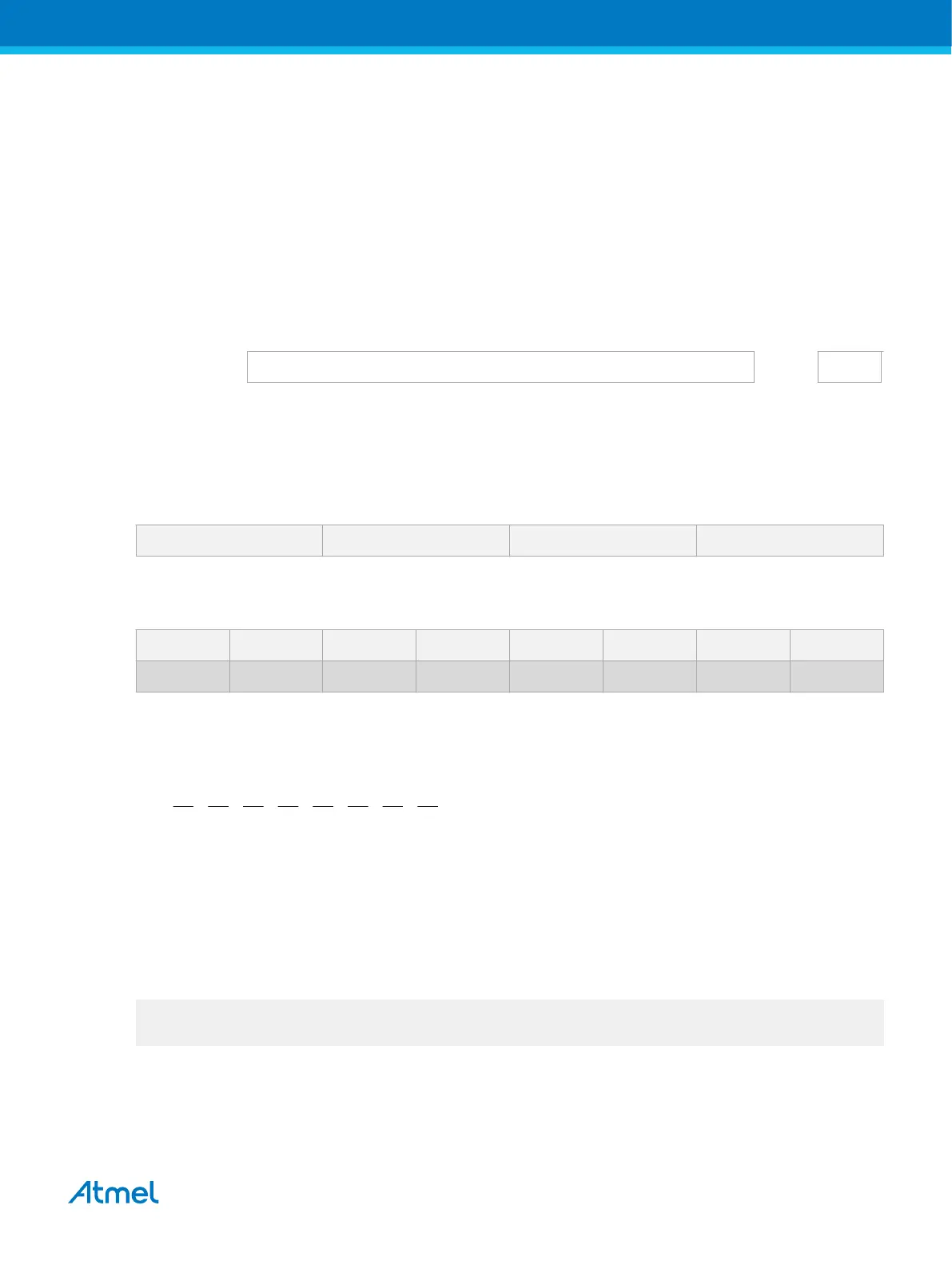

Syntax: Operands: Program Counter:

(i) LSR Rd 0 ≤ d ≤ 31 PC ← PC + 1

16-bit Opcode:

1001 010d dddd 0110

78.2. Status Register (SREG) and Boolean Formula

I T H S V N Z C

– – – ⇔ ⇔ 0 ⇔ ⇔

S N ⊕ V, for signed tests.

V N ⊕ C, for N and C after the shift.

N 0

Z R7 • R6 • R5 • R4 • R3 • R2 • R1 • R0

Set if the result is $00; cleared otherwise.

C Rd0

Set if, before the shift, the LSB of Rd was set; cleared otherwise.

R (Result) equals Rd after the operation.

Example:

add r0,r4 ; Add r4 to r0

lsr r0 ; Divide r0 by 2

Words 1 (2 bytes)

Cycles 1

Atmel AVR Instruction Set Manual [OTHER]

Atmel-0856L-AVR-Instruction-Set-Manual_Other-11/2016

122

Loading...

Loading...