IPC@CHIP SC123/SC143

Hardware Manual V1.06 [18.02.2010]

©2000-2008 BECK IPC GmbH Page 11

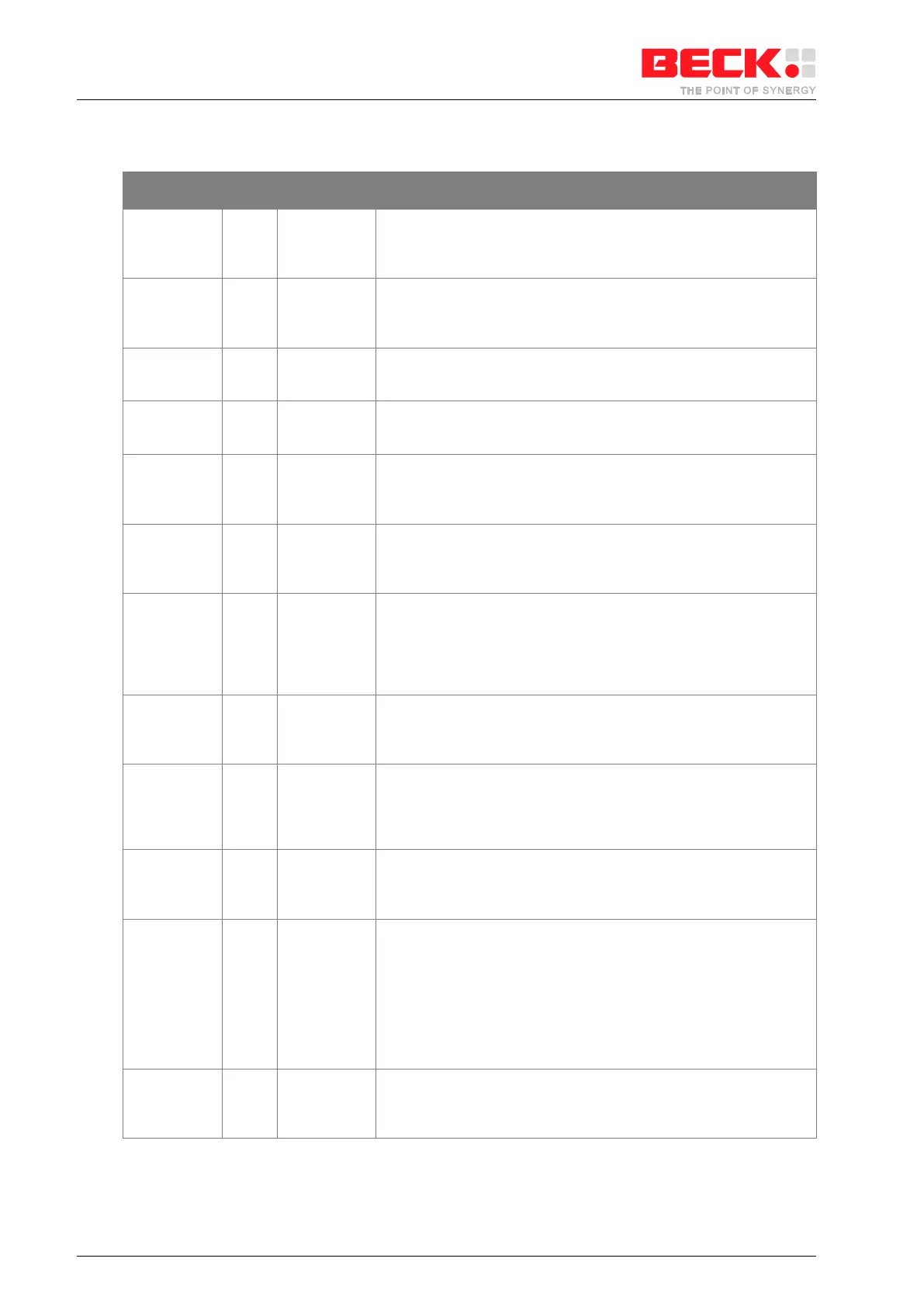

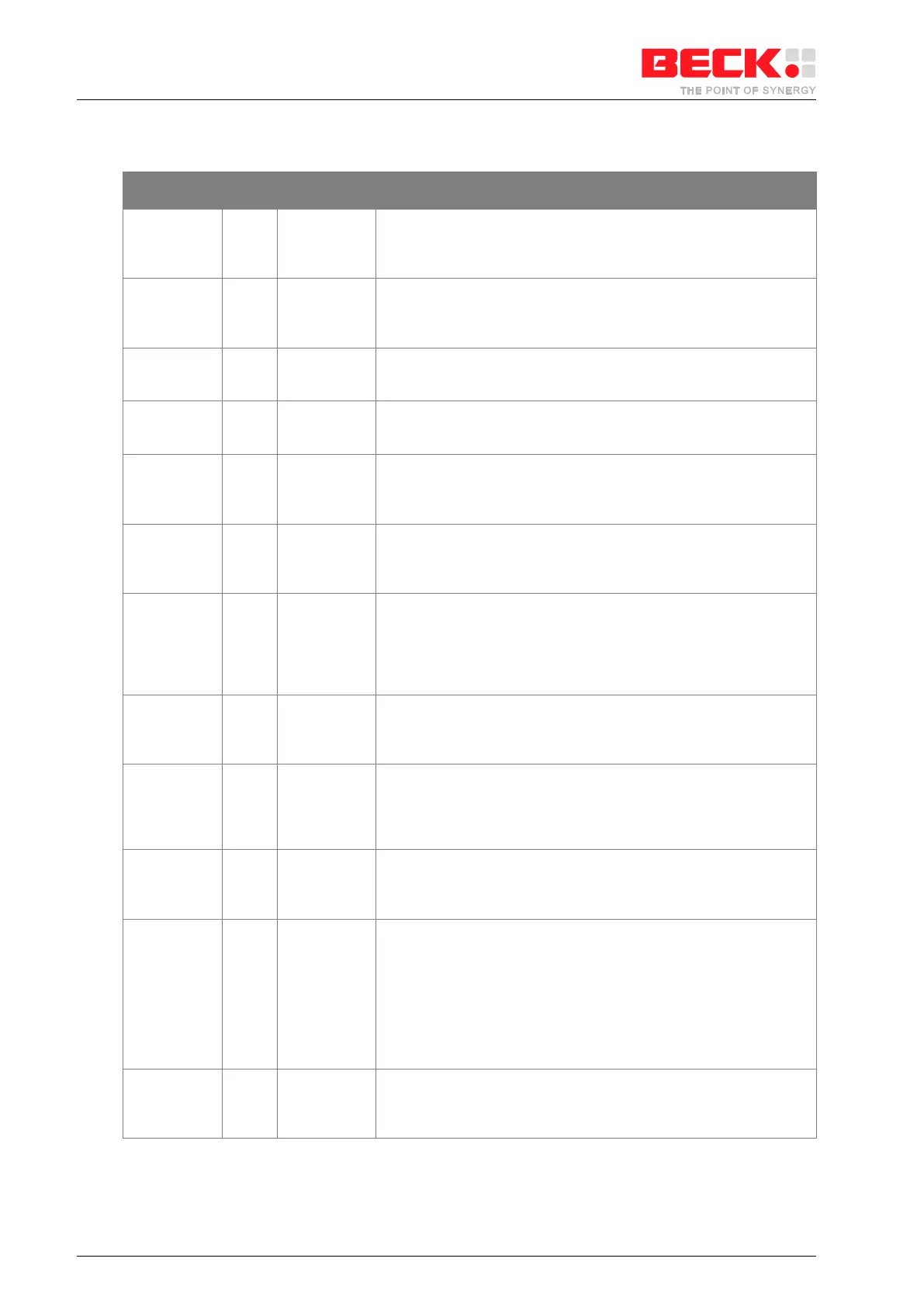

4.2 System Interface

CPU Clock Output

This pin is driven from the output of the internal PLL.

If it used as output, don’t connect anything with more than 1pF

capacitive load ! See chapter 12.

PLL Bypass Input (Active LOW with Pull-up)

PLLBYP# is not supported anymore! See history, chapter 14.

This input, when pulled LOW, bypasses the internal PLL and uses

the CPUCLK pin as the source for the CPU.

Write Output (Active LOW with Pull-up)

This pin indicates that the current bus cycle is a memory or I/O write

cycle.

Read Output (Active LOW with Pull-up)

This pin indicates that the current bus cycle is a memory or I/O read

cycle.

Write High Output (Active Low with Pull-up)

This pin indicates that the current bus cycle is a memory or I/O write

cycle and that the upper byte is being driven with valid data.

It can be used as BHE# (see chapter 5).

Write Low Output (Active LOW with Pull-up)

This pin indicates that the current bus cycle is a memory or I/O write

cycle and that the lower byte is being driven with valid data.

It can be used as A0 (see chapter 5).

Hold (Active HIGH)

Hold is not supported anymore! See history, chapter 14.

This pin can be used as HOLD input. When driven HIGH by an

external bus master, the CPU responds with HLDA and releases the

bus for external use.

It can also be used as PIO[17].

Hold Acknowledge (Active HIGH)

HLDA is not supported anymore! See history, chapter 14.

This pin goes HIGH to indicate the bus has been released for use by

an external bus master.

Asynchronous Ready (Active HIGH)

This pin can be used with an external ready source. ARDY is double

synchronized internally using the falling edge of CPUCLK. It can be

used to extend external accesses.

It can also be used as PIO[6].

Lower Chip Select (Schmitt Trigger Input Active LOW with Pull-up)

LCS# is not supported anymore! See history, chapter 14.

This pin is used by an external bus master to enable reading and

writing the internal SRAM.

Reset Input (Schmitt Trigger Input, Active LOW with Pull-up)

This pin causes the CPU to perform a reset. When this pin is

asserted, the CPU immediately terminates any current bus cycles,

resets internal logic and prepares for executing code at the reset

address FFFFE0h.

RSTIN# is synchronized internally and extended internally to allow

~200 ms for the startup configuration (chapter 5) to settle to the

values driven by there individual resistors. This input is provided

with a Schmitt trigger to power-on via an RC network.

Reset Output (Active LOW)

This pin indicates whether the CPU is being reset. It indicates that

the internal logic is being reset and is to be used to reset any

external peripherals.

Loading...

Loading...