IPC@CHIP SC123/SC143

Hardware Manual V1.06 [18.02.2010]

©2000-2008 BECK IPC GmbH Page 26

6.1.4 Peripheral Accesses through the Address-/Databus

This chapter gives an overview over accesses of the address-/databus to the periphery. The accesses are

described only in principle and for a better understanding. Exact timings are documented in chapter 8.3, AC

Characteristics.

Note: RD# and WR# can be low before the access and can stay low after the access, while internal accesses

of the CPU are in progress.

A marks positions, where wait states can stretch the access.

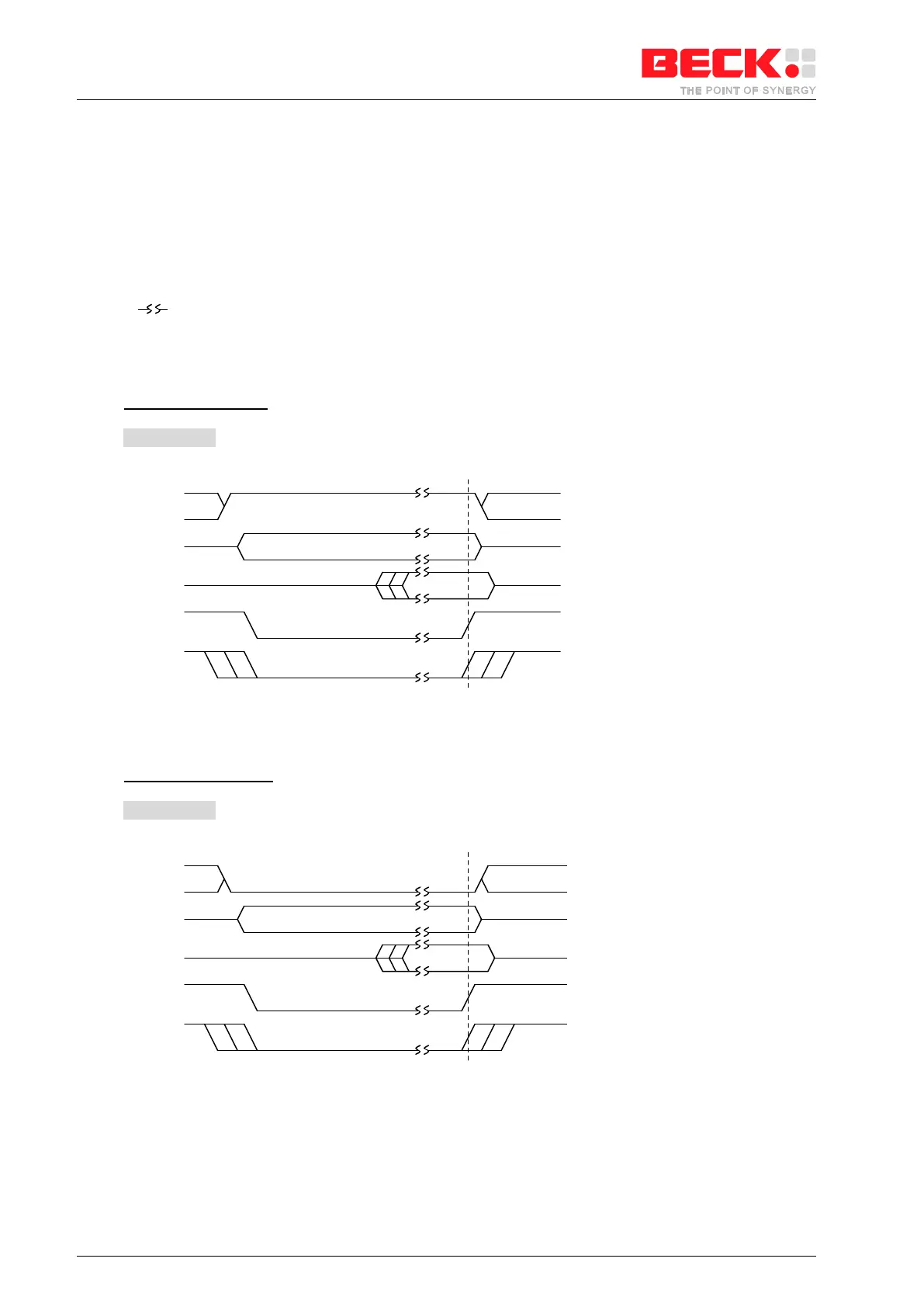

a) CSBE = 0 (Chip Select Byte Enable = A0/BHE#, see chapter 5.2 Address Pins)

Byte read from 0xC00

e.g.

Figure 6-3: 8 Bit read access from C00

h

, CSBE = 0, Read = 0x55

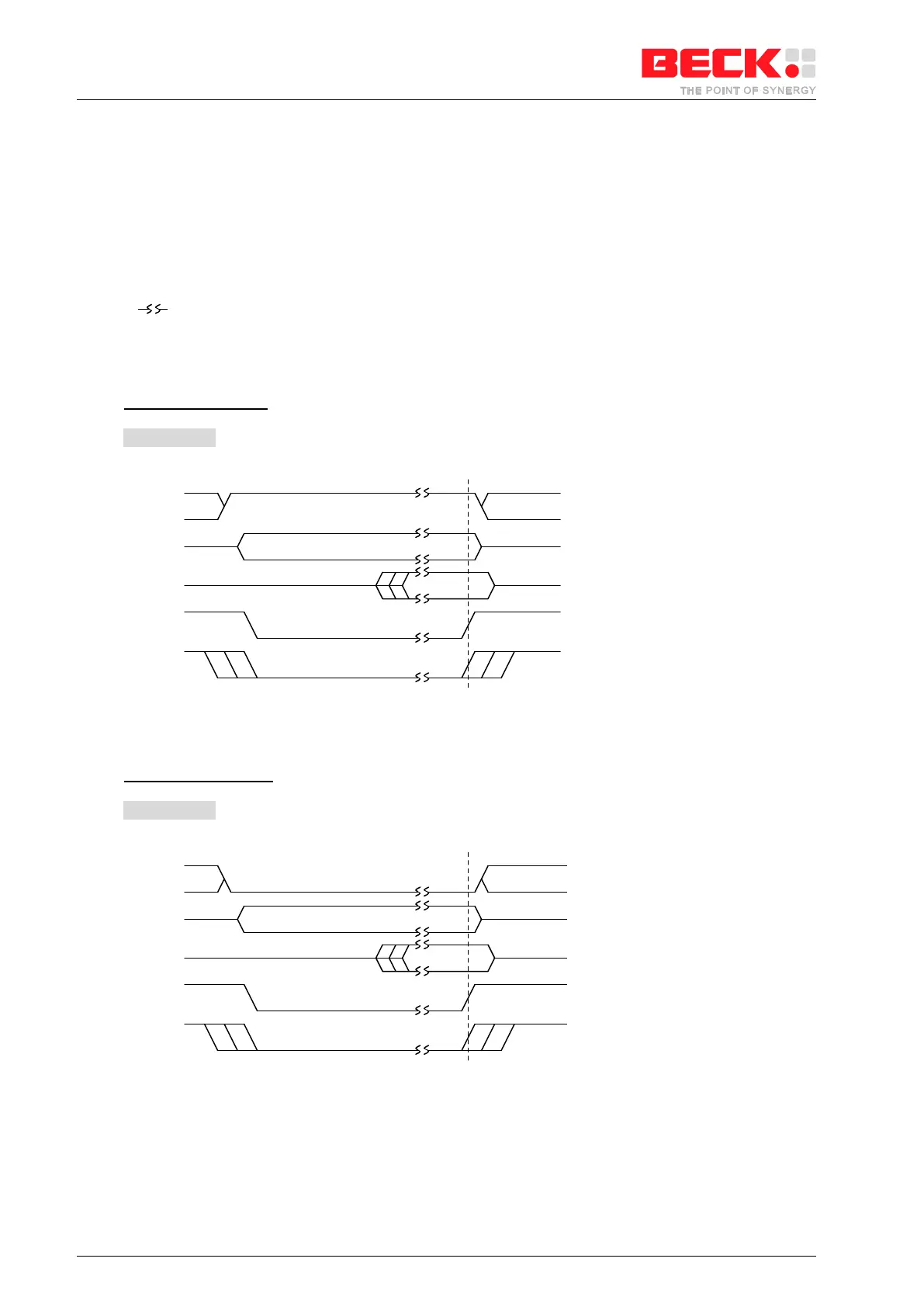

Word read from 0xC00

e.g.

Figure 6-4: 16 Bit read access from C00

h

, CSBE = 0, Read = 0x1234

Loading...

Loading...