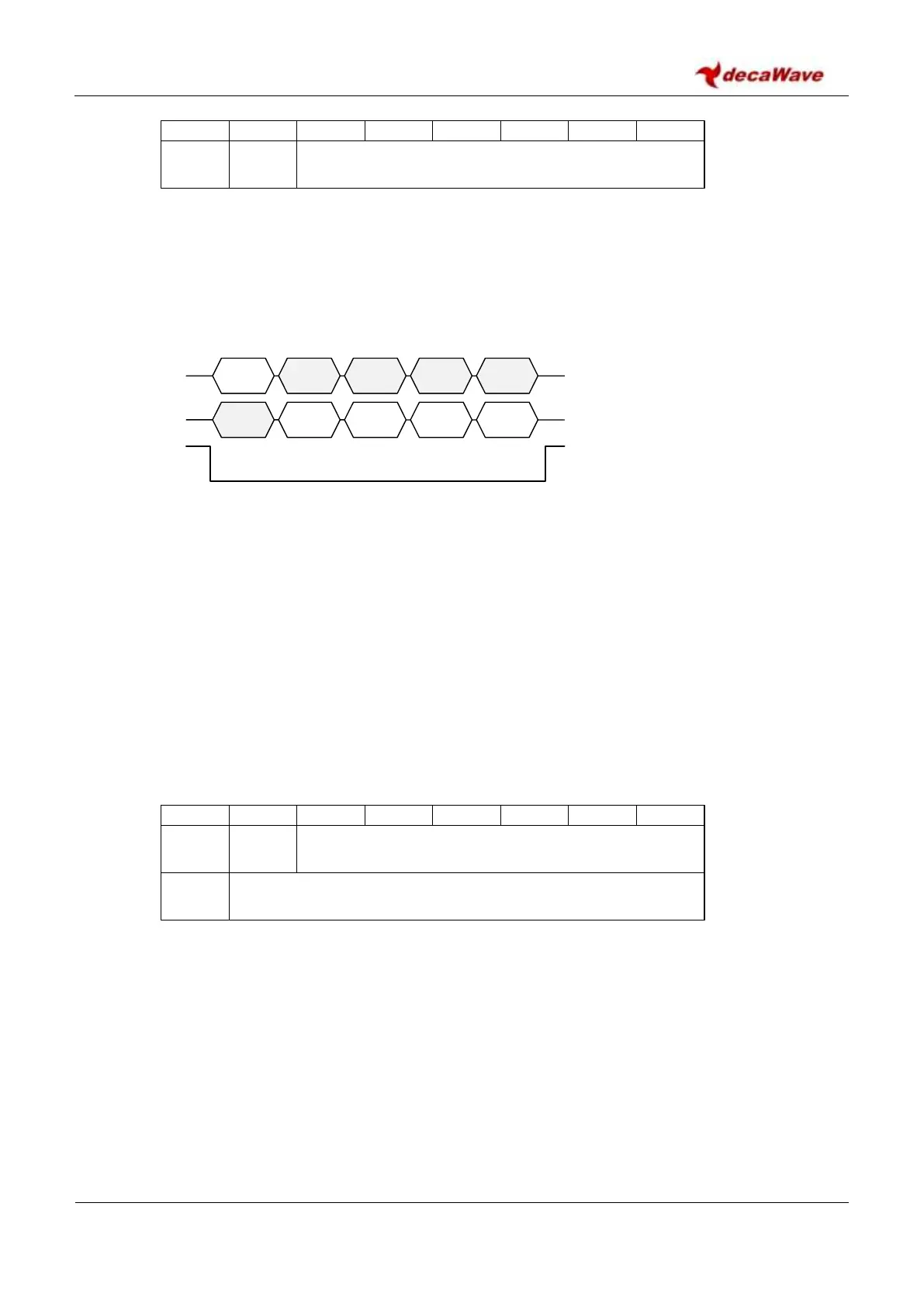

Figure 2: Single octet header of the non-indexed SPI transaction

The remaining octets of the transaction, the transaction body, immediately following this one-octet header

are read from (or written to) the selected register file beginning at index zero. Figure 3 shows an example of

a non-indexed read from the Device ID register using the single octet header.

Figure 3: Example non-indexed read of the Device ID register (0x00)

Note: The octets of a multi-octet value are transferred on the SPI interface in octet order beginning with

the low-order octet. This is shown in Figure 3.

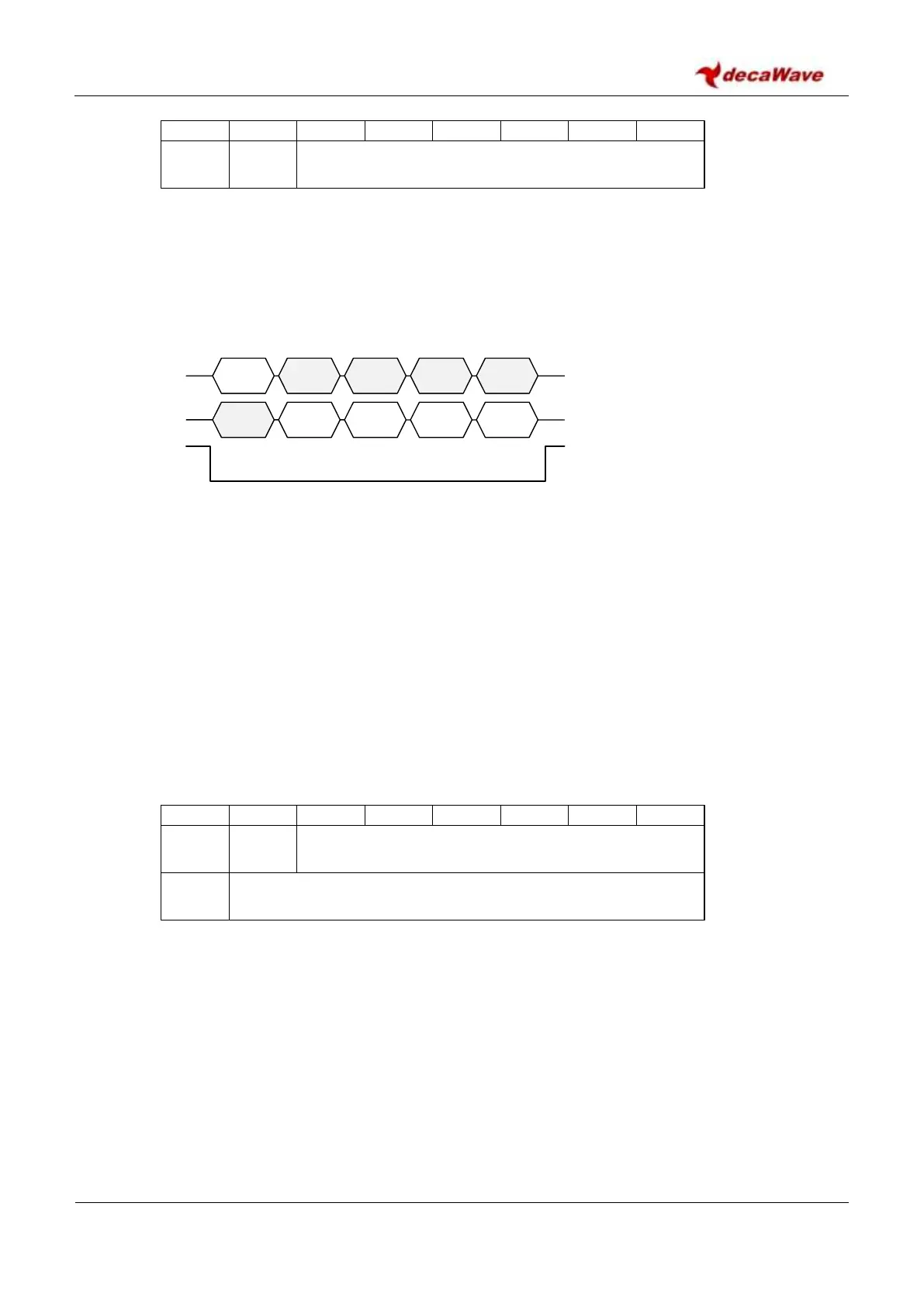

2.2.1.2.1 SPI transaction with a 2-octet header

Figure 4 shows the fields within the two octet transaction header of a short-indexed SPI transaction. Bit-6 of

the first octet is 1 indicating that a sub-index is present. The register (file) ID in the first octet selects the top

level address of the DW1000 parameter block being accessed. In the second octet bit-7 is zero indicating

that a further transaction header octet is not present and that the remaining 7 bits of octet-2 are a short

sub-index into the register file.

Figure 4: Two octet header of the short indexed SPI transaction

The remaining octets of the transaction, the transaction body, immediately following this two-octet header

are read from (or written to) the selected register file beginning at the selected index address 0 to 127.

Figure 5 shows an example of an indexed read from the Device ID register using the two octet transaction

header.

7 6 5 4 3 2 1 0

Operation:

0 = Read

1 = Write

Bit = 0, says

sub-index is

not present

Register file ID – Range 0x00 to 0x3F (64 locations)

Bit number:

Meaning:

Transaction Header

Octet

7 6 5 4 3 2 1 0

Operation:

0 = Read

1 = Write

Bit = 1, says

sub-index is

present

Register file ID – Range 0x00 to 0x3F (64 locations)

Extended

Address:

0 = no

7-bit Register File sub-address, range 0x00 to 0x7F (128 byte locations)

Bit number:

Meaning:

Transaction Header

Octet 1

Octet 2

Non sub indexed read from register

Loading...

Loading...