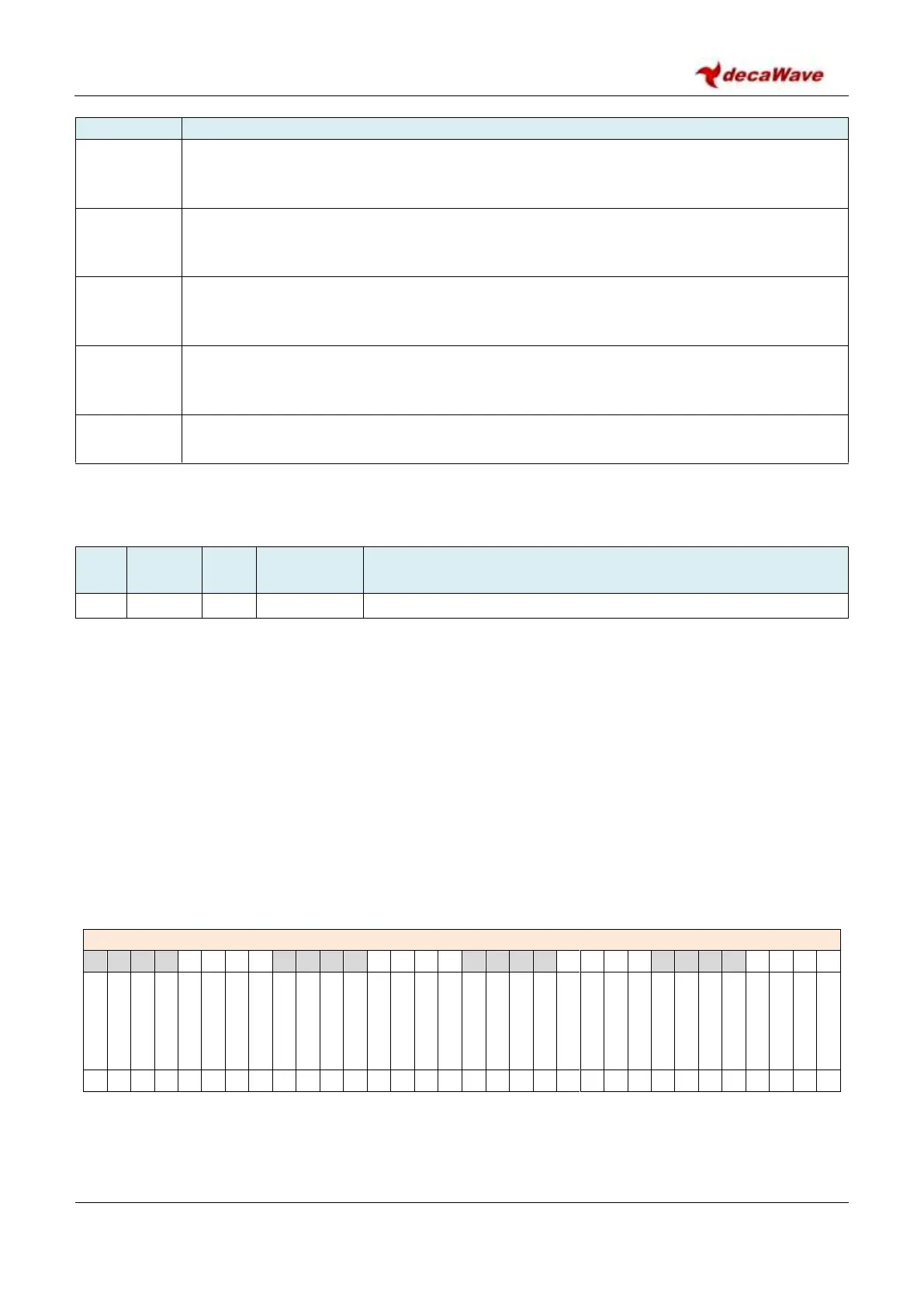

Description of fields within Register file: 0x0E – System Event Mask Register

MRXSFDTO

reg:0E:00

bit:26

Mask Receive SFD timeout event. When MRXSFDTO is 0 the RXSFDTO event status bit will not

generate an interrupt. When MRXSFDTO is 1 and the RXSFDTO event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

MHPDWARN

reg:0E:00

bit:27

Mask Half Period Delay Warning event. When MHPDWARN is 0 the HPDWARN event status

bit will not generate an interrupt. When MHPDWARN is 1 and the HPDWARN event status

bit is 1, the hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask Transmit Buffer Error event. When MTXBERR is 0 the TXBERR event status bit will not

generate an interrupt. When MTXBERR is 1 and the TXBERR event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask Automatic Frame Filtering rejection event. When MAFFREJ is 0 the AFFREJ event status

bit will not generate an interrupt. When MAFFREJ is 1 and the AFFREJ event status bit is 1,

the hardware IRQ interrupt line will be asserted to generate an interrupt.

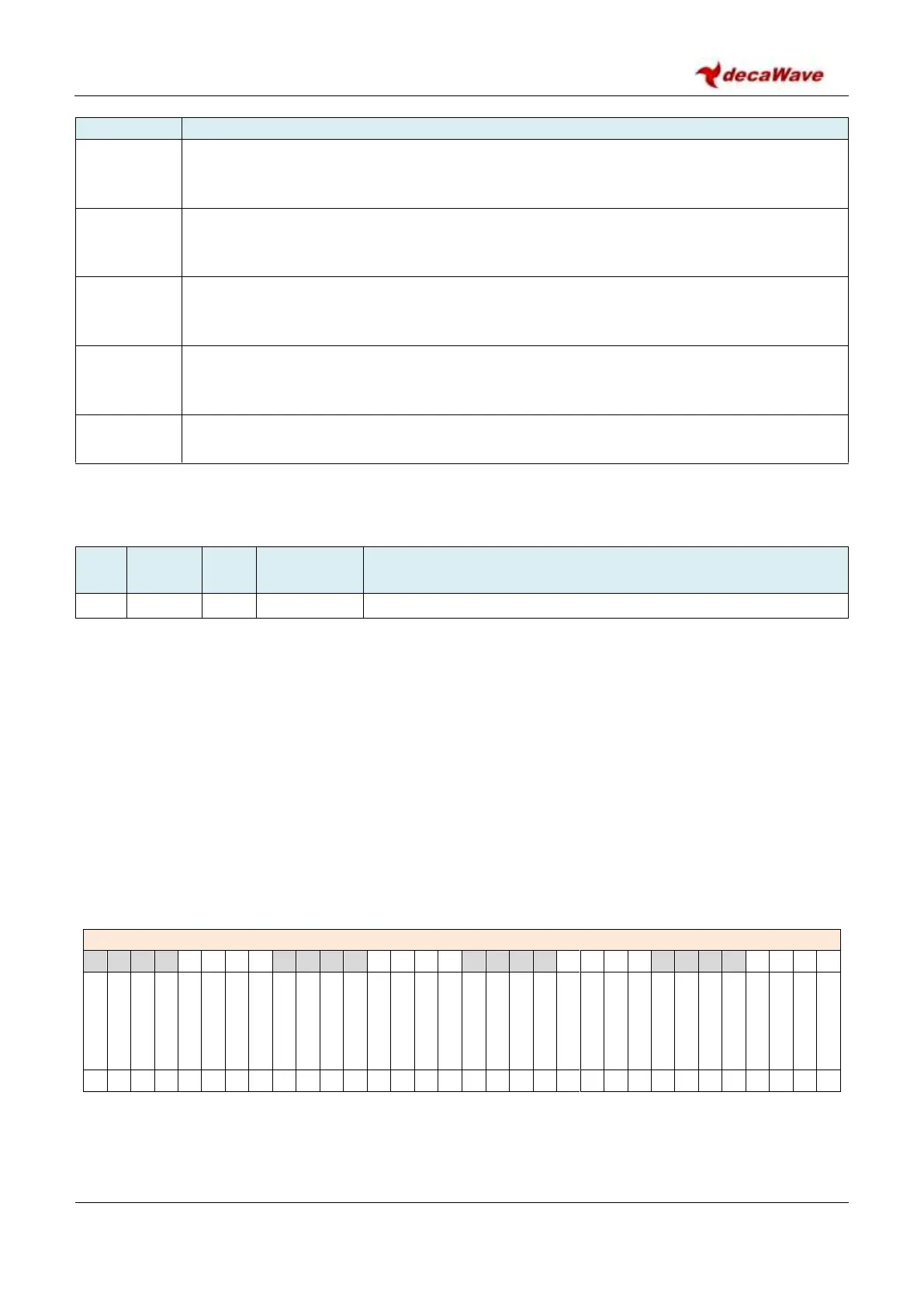

7.2.17 Register file: 0x0F – System Event Status Register

System Event Status Register

Register map register file 0x0F is the system event status register, SYS_STATUS. It contains status bits that

indicate the occurrence of different system events or status changes. It is possible to enable particular

events as interrupt sources, by employing the SYS_MASK, Register file: 0x0E – System Event Mask Register,

so that the setting of the event status bit will generate an interrupt, asserting the hardware IRQ output line.

This can be used, for example, to allow the host processor to enter a low-power state during frame

transmission or reception awaiting an interrupt to wake upon the completion of the TX or RX activity.

Reading the SYS_STATUS register returns the state of the status bits. Generally these event status bits are

latched so that the event is captured. Such latched bits need to be explicitly cleared by writing a '1' to the bit

position (writing '0' has no effect).

The SYS_STATUS register contains the system event status bits identified and described below:

REG:0F:00 – SYS_STATUS – System Status Register (octets 0 to 3)

Loading...

Loading...