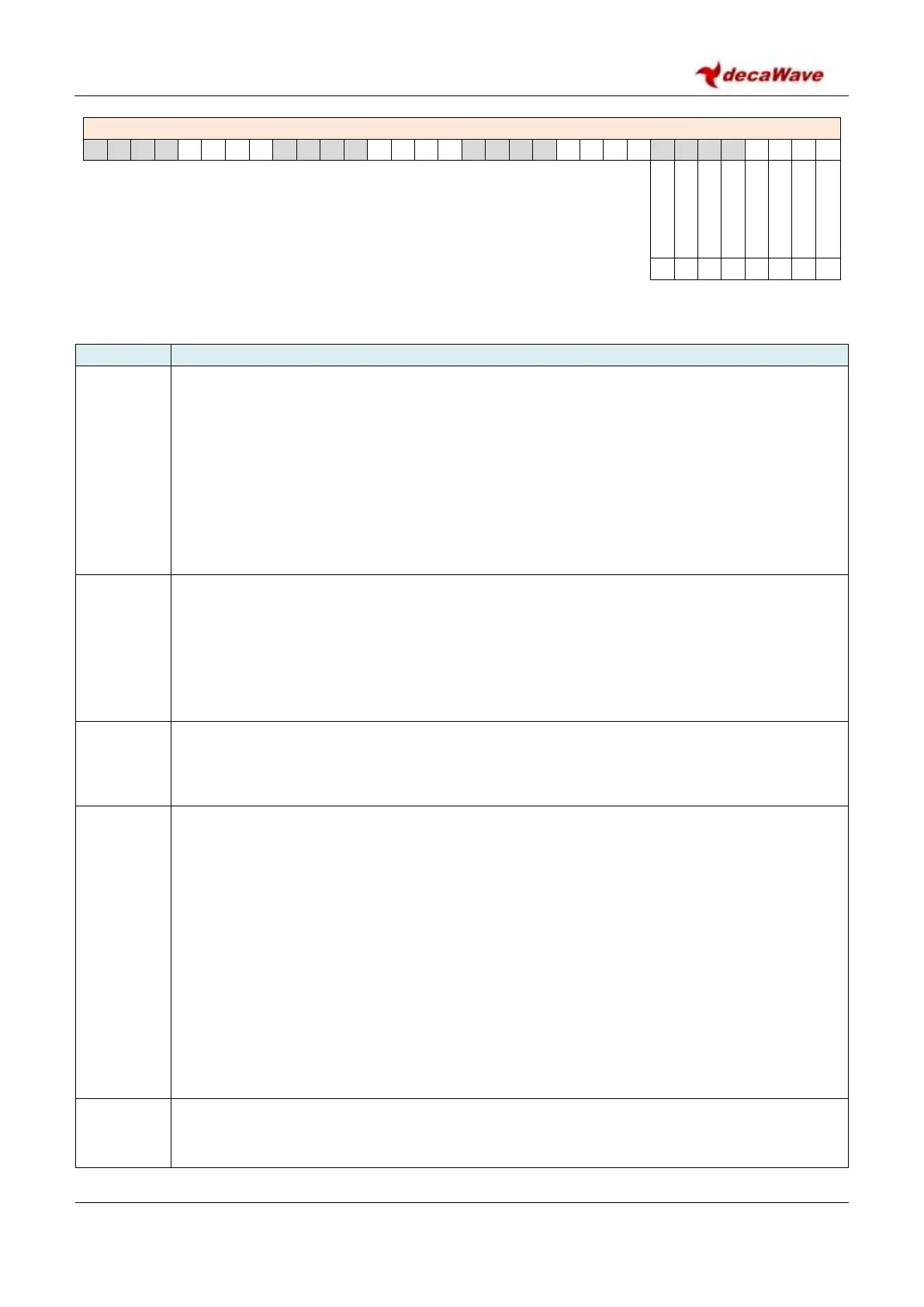

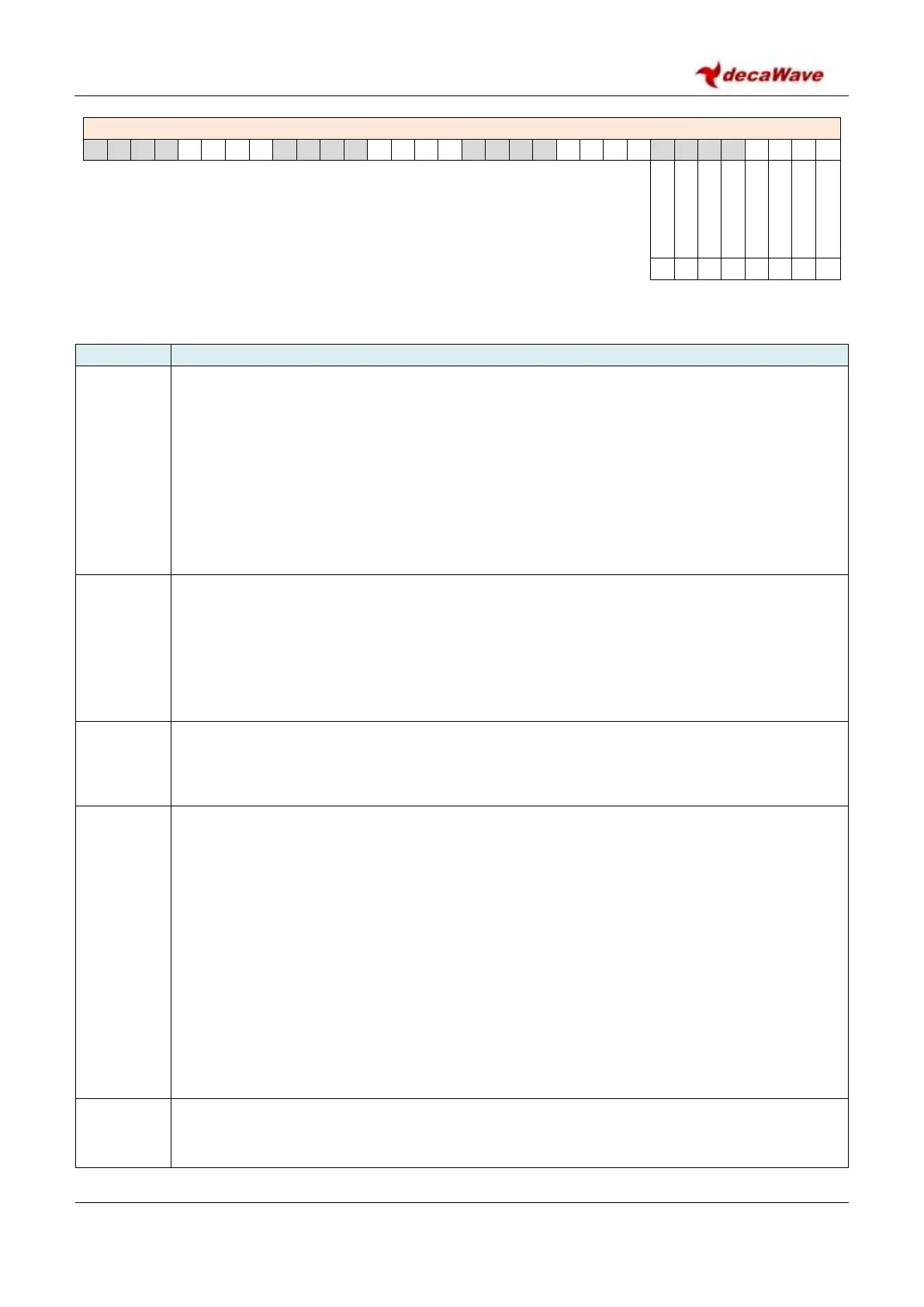

REG:0F:04 – SYS_STATUS – System Status Register (octet 4)

The system event status bits of the SYS_STATUS register identified above are individually described below:

Description of fields within Register file: 0x0F – System Event Status Register

Interrupt Request Status. This is a READ ONLY status flag – it cannot be cleared or overwritten.

Whenever a status bit in Register file: 0x0F – System Event Status Register is activated (i.e. has

a value of 1) and the corresponding bit in Register file: 0x0E – System Event Mask Register is

enabled (i.e. has a value of 1 also) then the IRQ interrupt request line will be driven to its active

ON level. If there are no active mask enabled status bits then the IRQ interrupt request line will

be set to its inactive OFF level. This IRQS flag reflects the overall status of interrupts. If there

are any unmasked interrupt sources active then the IRQS bit will be 1 (and IRQ interrupt

request line will be at its active ON level) the otherwise IRQS will be zero (and IRQ interrupt

request line at its OFF level). The polarity of the IRQ interrupt request line is controllable via

the HIRQ_POL configuration bit in Register file: 0x04 – System Configuration.

Clock PLL Lock. The CPLOCK event status bit indicates that the digital clock PLL has locked.

This may be used as an interrupt to indicate that the DW1000 clock is operating at full speed,

after which the SPI can be run at its maximum rate also. The CPLOCK bit is cleared by writing a

1 to it. The clock PLL lock status is also available via the CPLLLOCK status bit in Sub-Register

0x28:2C – RF_STATUS.

Note: The PLLLDT bit in Register file 0x24:00 –EC_CTRL should be set to ensure reliable

operation of this CPLOCK bit.

External Sync Clock Reset. This event status bit is set when the system counter is reset as a

result of the reception of an external synchronisation clock reset signal on the SYNC pin. The

ESYNCR flag bit is cleared by writing a 1 to it. Section 6.1 – External Synchronisation describes

this feature.

Automatic Acknowledge Trigger. This status event status bit is set when frame filtering is

enabled and a data frame (or MAC command frame) is received (correctly addressed and with

a good CRC) with the acknowledgement request bit set in its frame control field.

If the automatic acknowledgement is enabled (by the AUTOACK bit in Register file: 0x04 –

System Configuration) then the AAT bit can be used during receive interrupt processing to

detect that acknowledgement is in progress and so avoid taking any action until the

transmission of the acknowledgement is completed – an event that might be detected by

awaiting the TXFRS (Transmit Frame Sent) status interrupt.

If automatic acknowledgement is not enabled, then the AAT status bit must be ignored.

The AAT bit can be cleared explicitly by writing a 1 to it. It is also automatically cleared by the

next receiver enable, (including those caused by the RXAUTR auto-re-enable).

Transmit Frame Begins. This event status bit is set at the start of a frame transmission as the

transmitter begins to send preamble. The TXFRB bit is automatically cleared at the next

transmitter enable. It can also be cleared explicitly by writing a 1 to it.

Loading...

Loading...