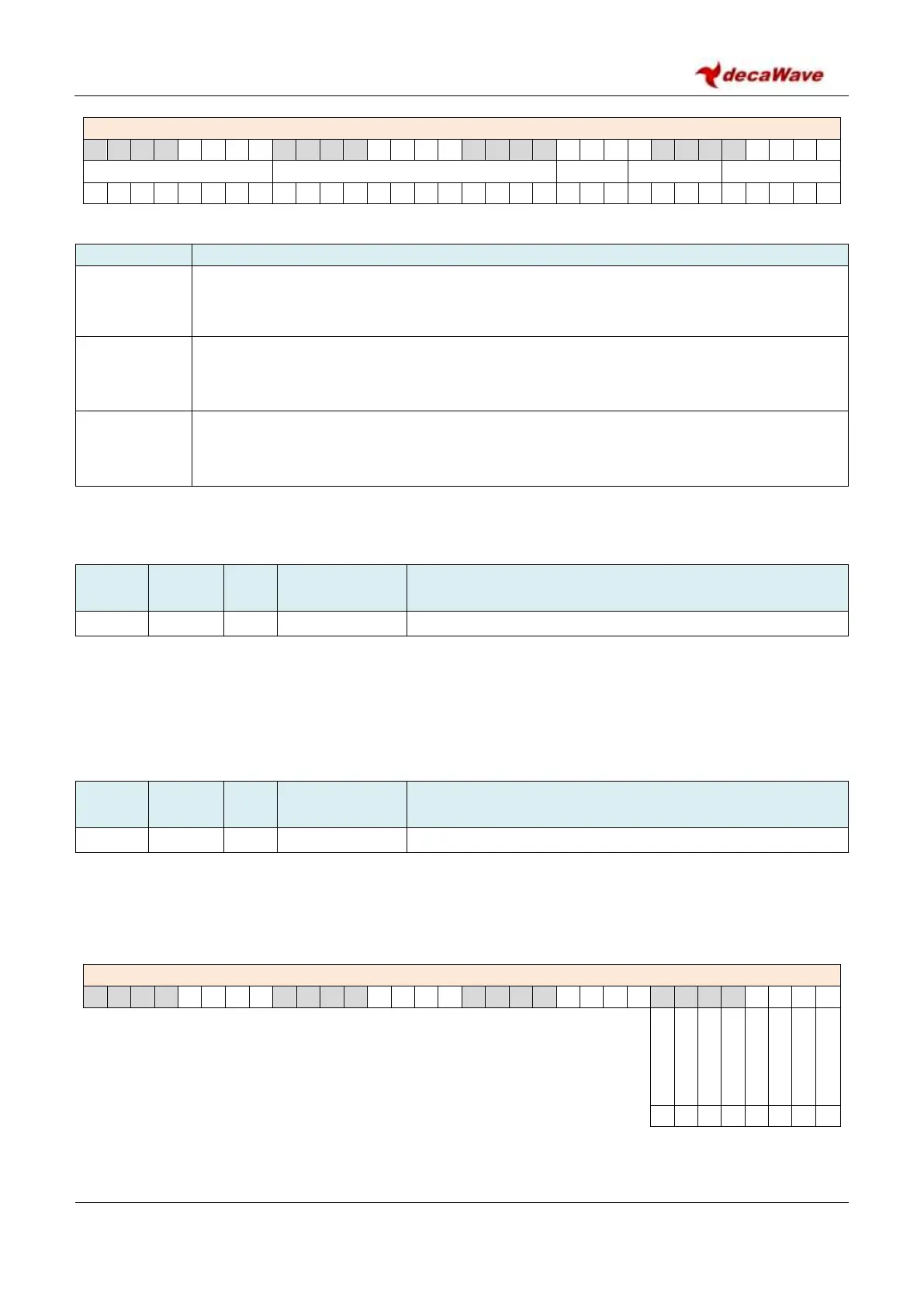

REG:28:0C – RF_TXCTRL – Transmitter Analog Settings

Definition of the bit fields within Sub-Register 0x28:0C– RF_TXCTRL:

Description of fields within Sub-Register 0x28:0C– RF_TXCTRL

Reserved

reg:28:0C

bits:31:12,4:0

These fields are reserved. Program only as directed in Table 38.

TXMTUNE

reg:28:0C

bits:8:5

Transmit mixer tuning register. This register should be set as directed in Table 38. It is

possible to tune to optimise performance for individual part as described in section 8.2.2 –

Other TX adjustments to consider.

Transmit mixer Q-factor tuning register. This register should be set as directed in Table 38.

It is possible to tune to optimise performance for individual part as described in section

8.2.2 – Other TX adjustments to consider.

7.2.41.5 Sub-Register 0x28:10 – RF_RES2

Register file: 0x28 – Analog RF configuration block, sub-register 0x10 is a reserved register. Please take care

not to write to this register as doing so may cause the DW1000 to malfunction.

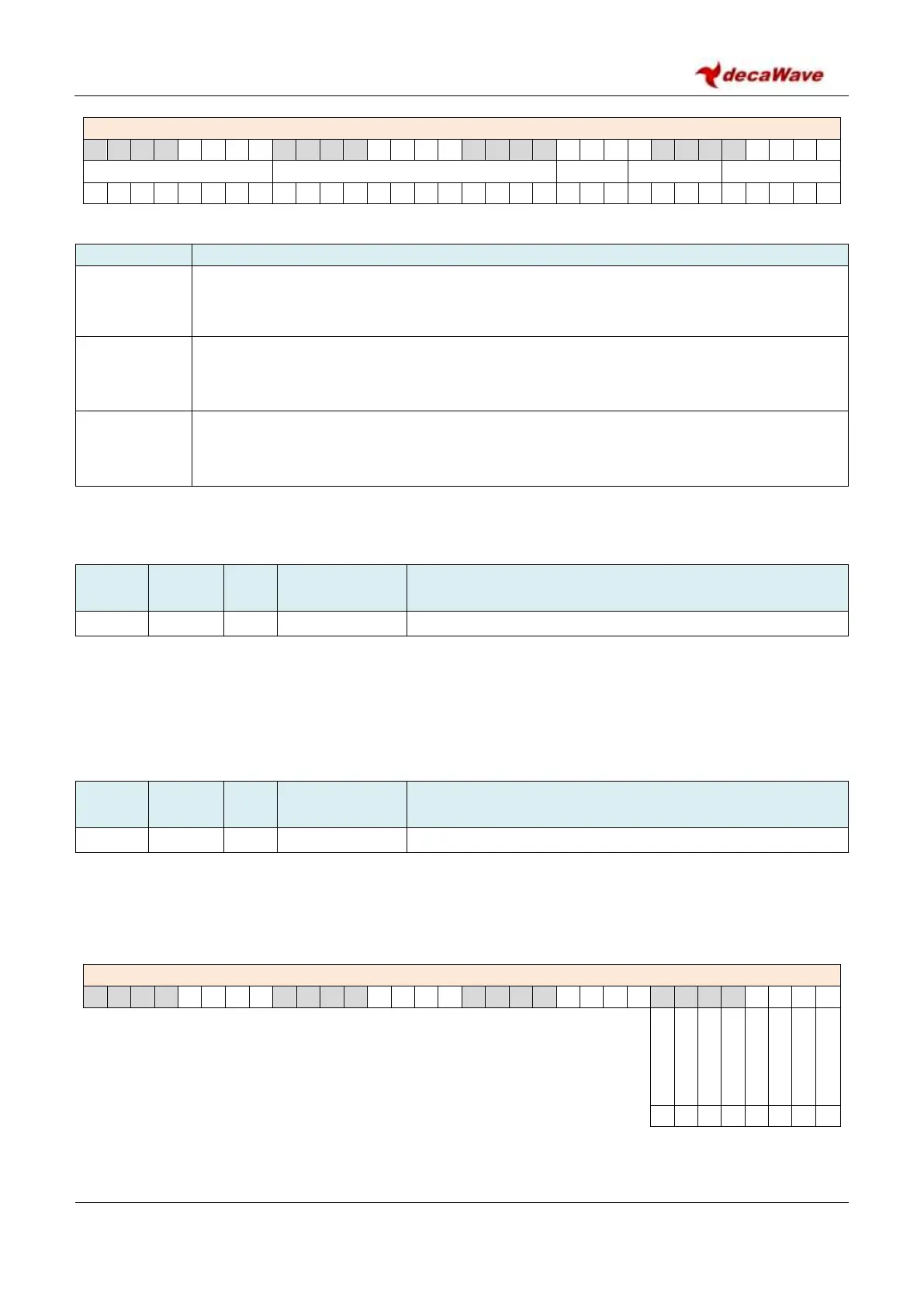

7.2.41.6 Sub-Register 0x28:2C – RF_STATUS

Register file: 0x28 – Analog RF configuration block, sub-register 0x2C is the PLL lock status register.

Generally it is not necessary to monitor this register. However it may be useful as a diagnostic in the event

of problems. The RF_STATUS register contains the following status bits identified and described below:

REG:28:2C – RF_STATUS – RF Status Register

The bits of the RF_STATUS register identified above are individually described below:

Loading...

Loading...