7.2.40.11 Sub-Register 0x27:28 – DRX_CAR_INT

Carrier Recovery Integrator Register

Register file: 0x27 – Digital receiver configuration, sub-register 0x28 is a read-only 21 bit register.

The DW1000 receiver needs to compensate for frequency offsets between the timing references at the

transmitting device and itself to successfully receive a packet. Therefore, when a packet is successfully

received, the DW1000 has a sufficiently accurate estimate of the frequency offset.

This information is available in the carrier recovery integrator register, at address 0x27, offset 0x28. This is a

21 bit number with the lower 17 bits, the fractional part, and the upper 4 bits as the integer portion of the

number.

When a packet is successfully received, this register can be read and converted to the frequency error (in Hz)

using

F

offset

is the absolute frequency error in Hz. It can be converted to a clock offset (in ppm) by scaling by the

carrier frequency as follows

The minus sign is produced by the process of measuring the clock offset.

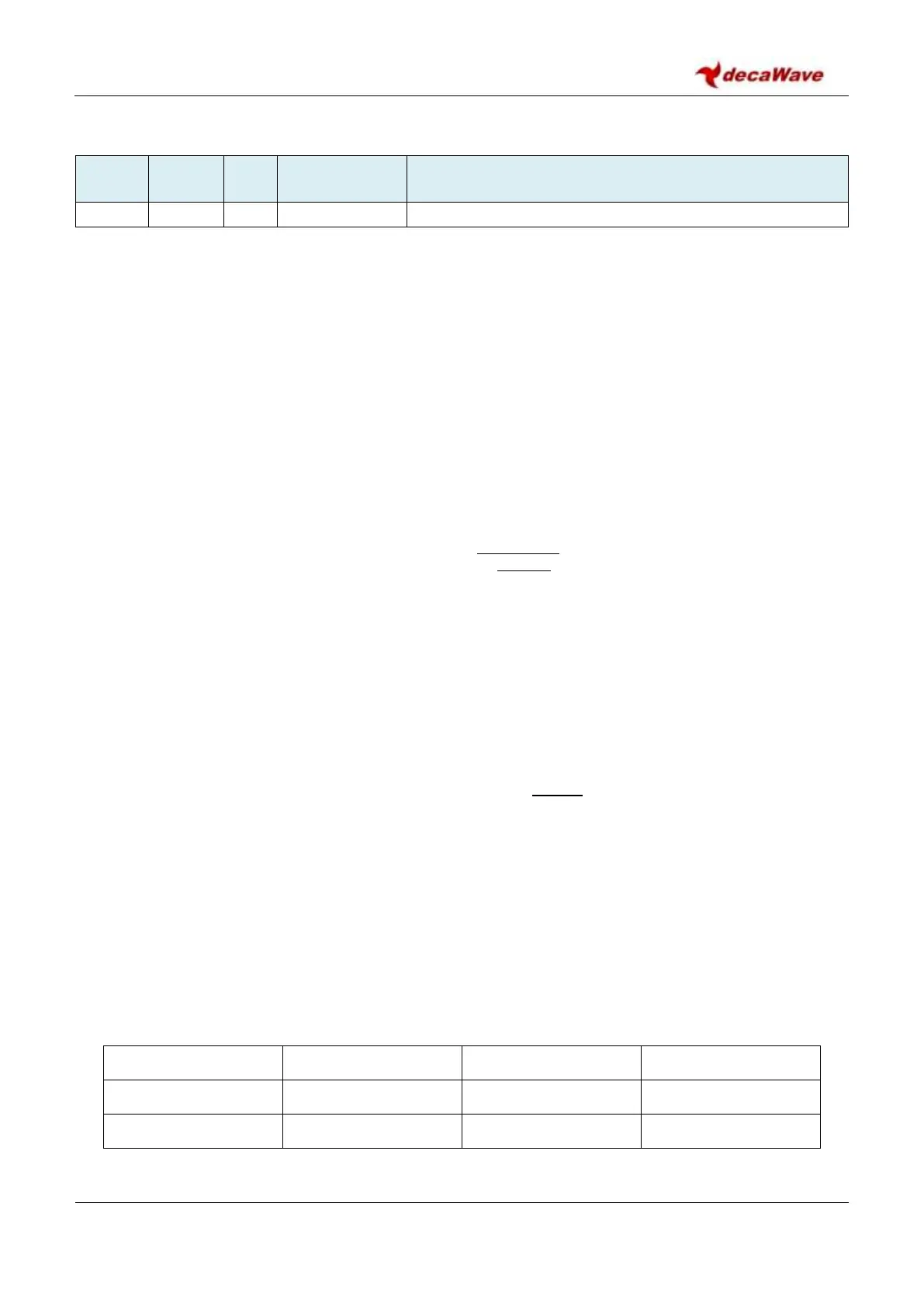

For a particular channel, the formulas reduce to multiplying the content of the carrier integrator register

with the appropriate constant from the table below:

Table 35: Constants for frequency offset calculation

Loading...

Loading...