PCIe Reset Signal (PERST#)

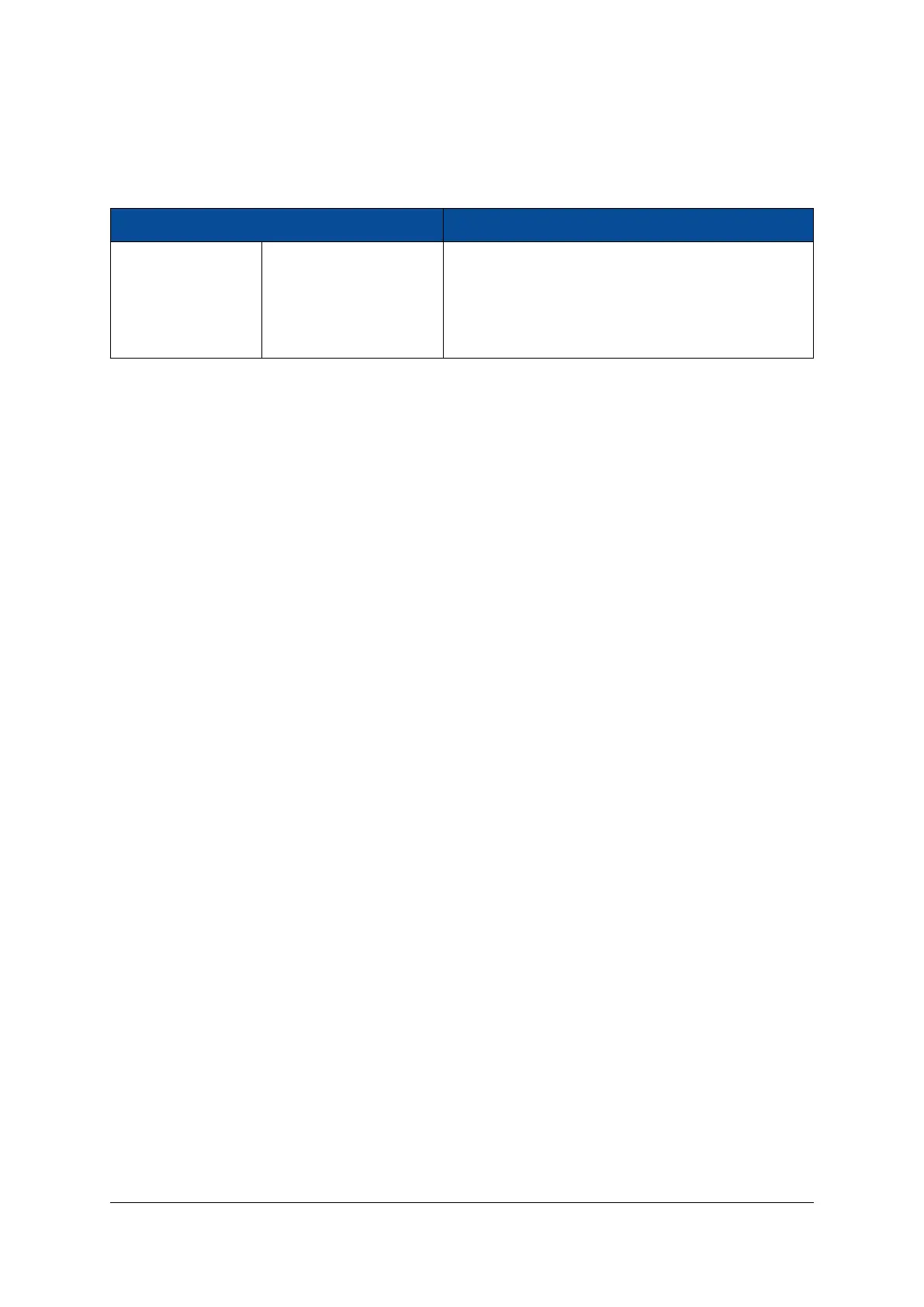

Table 6 lists the I/O pin exceptions on the Mercury XU5 SoC module related to the PCIe reset connection.

I/O Name Module Connector Pin Description

PS_MIO42_PERST# A-104 When the pin has a low value, its value is routed via

a 1 kΩ resistors to ETH0_TXD3_PERST# pin (MIO30)

and via a 47 kΩ resistor to IO_B65_L24_PERSTN_H8_N

(module pin B-126) for PCIe PERST# connection im-

plementation

Table 6: I/O Pin Exceptions - PERST#

When the Mercury XU5 SoC module is used in combination with a Mercury+ PE1 base board as a PCIe

device, the PERST# signal coming from the PCIe edge connector on the module connector pin A-104

(PS_MIO42_PERST#) is driven further to IO_B65_L24_PERSTN_H8_N and to ETH0_TXD3_PERST# (MIO30)

when its value is low.

When a PCIe block on the PL side is used, the PERST# signal is connected to the FPGA pin IO_B65_L24_PER-

STN_H8_N via a 47 kΩ resistor. In situations in which a custom board is used or PCIe functionality on the PL

side is not required, this FPGA pin can be used in the same manner as a regular I/O pin.

When a PCIe block on the PS side is used, the PERST# signal is routed via a 1 kΩ resistor to MIO30. This is

the default MIO pin used for the reset signal of the PCIe PS built-in block, therefore it was chosen for the

reset implementation. The Ethernet controller 0 is disabled when the PCIe hard block is used; note that any

other valid position for PERST# would have resulted in having the Ethernet controller disabled.

Using a PCIe block in the PL simultaneously with Gigabit Ethernet 0 interface on the PS side is possible.

Simultaneous usage of two PCIe endpoints on the PL and PS sides is not supported and was not tested on

Enclustra side.

In situations in which PCIe functionality is not required, PS_MIO42_PERST# pin can be used in the same

manner as a regular MIO pin.

Assembly Options and Migration between Modules

Depending on the equipped MPSoC device on the Mercury XU5 SoC module, the type and number of user

I/Os available on the module connector may differ.

On the Mercury XU5 SoC modules equipped with bigger MPSoC devices (ZU4/ZU5) there are four GTH

MGT transceiver lines and two differential clock inputs available, in addition to the GTR MGT lines and clocks

located on the PS side.

On the modules equipped with smaller MPSoC devices (ZU2/ZU3), the signals on the module connector are

routed to regular I/Os instead of GTH MGTs.

Table 7 presents the assembly variants for different product configurations. The signals on the module con-

nector are routed to different types of I/Os, depending on the product variant. To find out where exactly

these pins are routed, refer to the naming conventions for regular user I/Os (Section 2.9.1) and for MGT

signals (Section 2.10). Table 7 is also available in a separate file, FPGA Pinout Assembly Variants Excel Sheet

[5].

Figures 11, 12 and 13 depict the assembly variants information.

D-0000-445-001 21 / 64 Version 07, 25.07.2019

Loading...

Loading...