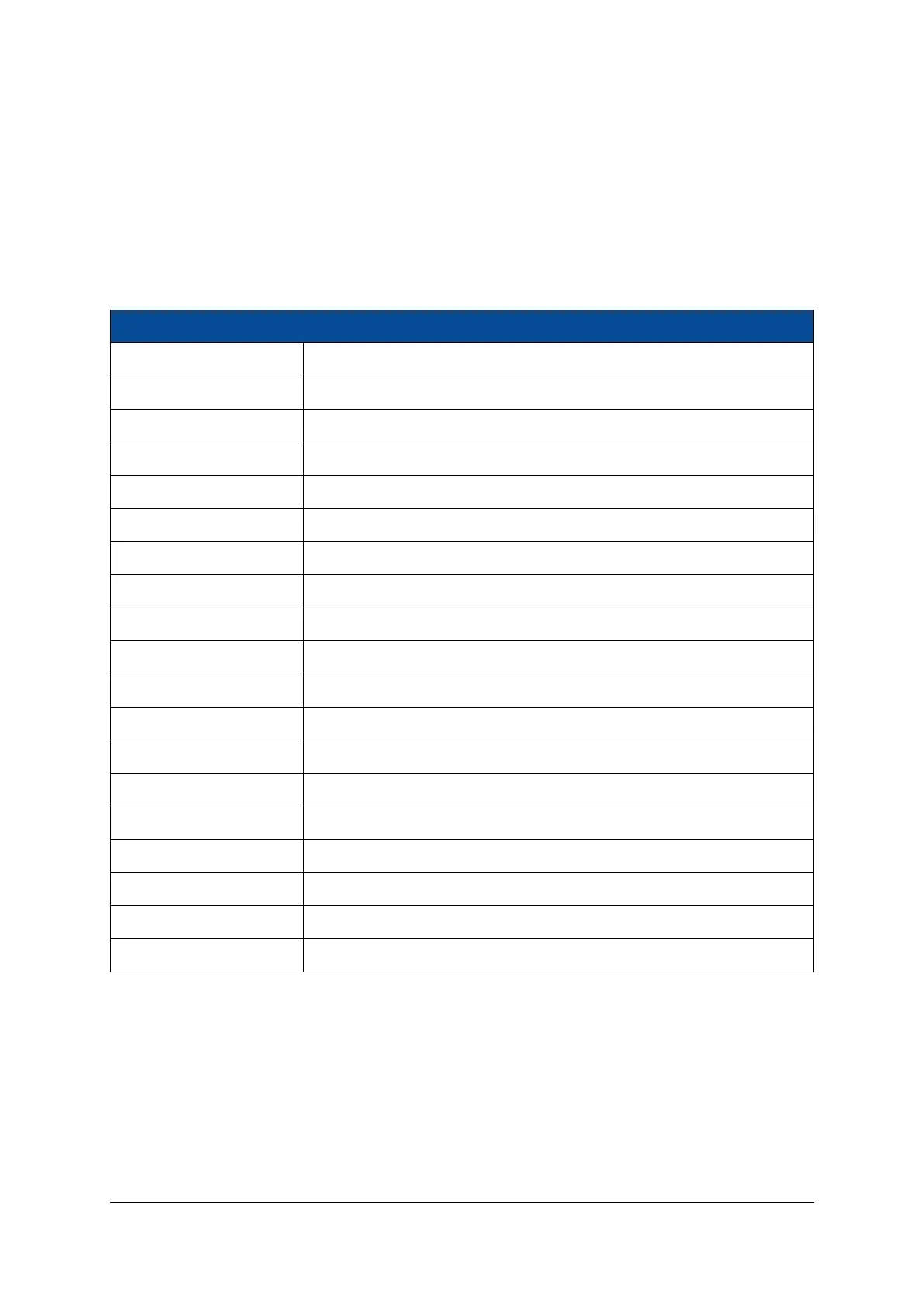

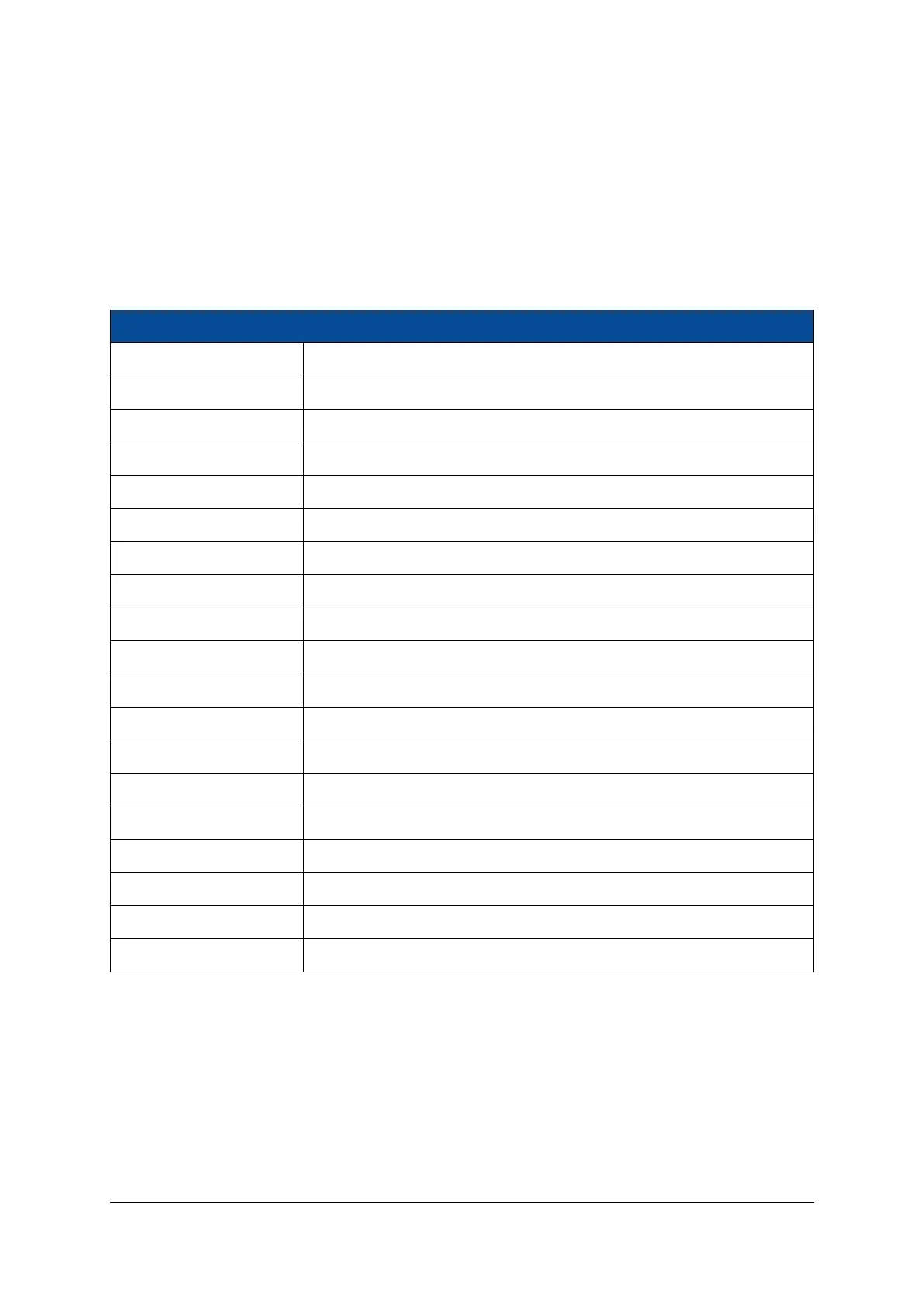

2.15.4 Parameters

Please refer to the Mercury XU5 SoC module reference design [2] for DDR4 settings guidelines.

The DDR4 SDRAM parameters to be set in the Vivado project are presented in Table 24.

The values given in Table 24 are for reference only. Depending on the equipped memory device on the

Mercury XU5 SoC module and on the DDR4 SDRAM frequency, the configuration may be different to the

one in the reference design. Please refer to the memory device datasheet for details.

Parameter Value

Memory type DDR4

DRAM bus width 64 bit (32 bit for ME-XU5-2CG-1E-D10H variant)

ECC Enabled (Disabled for ME-XU5-2CG-1E-D10H variant)

DRAM chip bus width 16 bits

DRAM chip capacity 4096-16384 Mbits

Bank group address count 1

Bank address count 2

Row address count 15-17

Column address count 10

Speed bin DDR4 2400T

Operating frequency 1200 MHz

CAS latency 17

CAS write latency 12

Additive latency 0

RAS to CAS delay 17

Precharge time 17

tRC 46.16 ns

tRASmin 32 ns

tFAW 30 ns

Table 24: DDR4 SDRAM (PS) Parameters

2.16 DDR4 SDRAM (PL)

The DDR4 SDRAM connected to the PL is mapped to I/O bank 64. The DDR bus width is 16-bit.

The DDR4 SDRAM memory connected to the PL supports different bandwidths depending on the equipped

MPSoC device:

• Speedgrade 1 devices: up to 2133 Mbit/s (1066 MHz)

D-0000-445-001 39 / 64 Version 07, 25.07.2019

Loading...

Loading...