2.20.3 External Connectivity

The Ethernet signal lines can be connected directly to the magnetics. Please refer to the Enclustra Module

Pin Connection Guidelines [11] for details regarding the connection of Ethernet signals.

2.20.4 MDIO Address

The MDIO address assigned to PHY 0 is 3, and the PHY can be configured via MIO pins 76-77.

2.20.5 PHY Configuration

The configuration of the Ethernet PHY is bootstrapped when the PHYs are released from reset. Make sure all

I/Os on the RGMII interface are initialized and all pull-up or pull-down resistors are disabled at that moment.

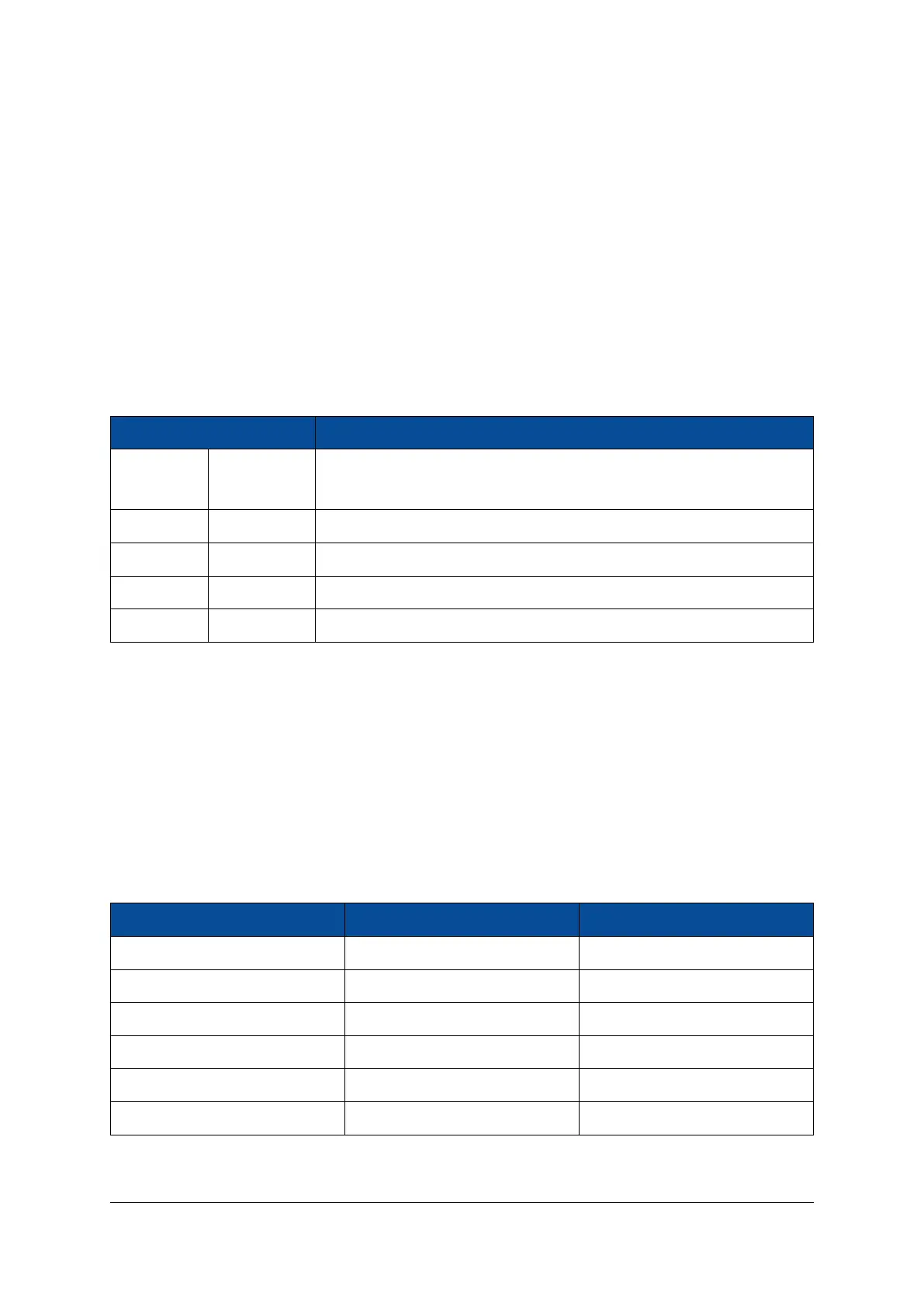

The bootstrap options of the Ethernet PHYs are set as indicated in Table 30.

Pin Signal Value Description

MODE[3-0] 1110 RGMII mode: advertise all capabilities (10/100/1000, half/full duplex) ex-

cept 1000Base-T half duplex.

PHYAD[2-0] 011 MDIO address 3

Clk125_EN 0 125 MHz clock output disabled

LED_MODE 1 Single LED mode

LED1/LED2 1 Active-low LEDs

Table 30: Gigabit Ethernet PHY (PS) Configuration - Bootstraps

For the Ethernet PHY configuration via the MDIO interface, the MDC clock frequency must not exceed 2

MHz.

2.20.6 RGMII Delays Configuration

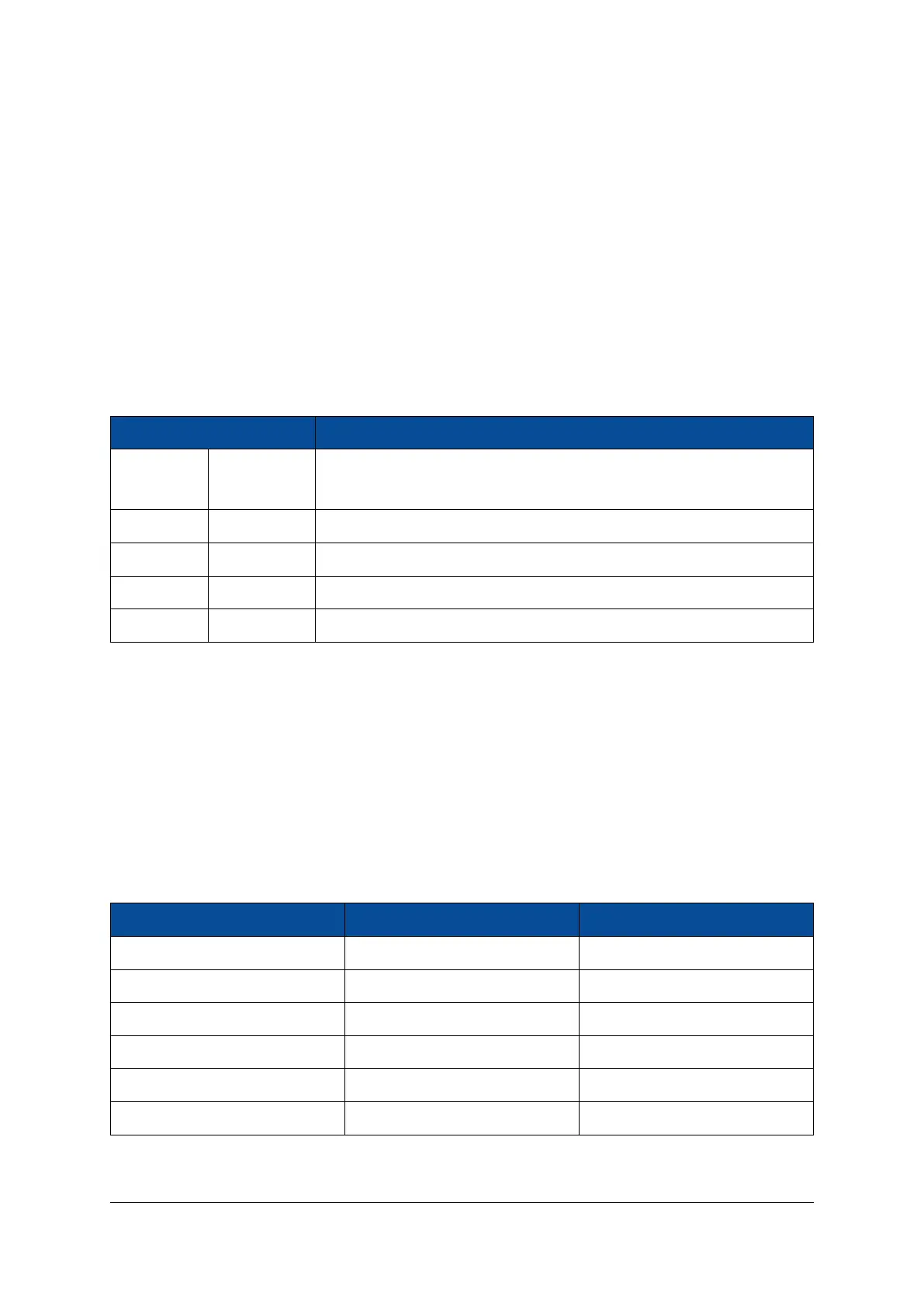

The Ethernet PHY (PS) is connected directly to the hard MAC controller present in the MPSoC device. In

order to achieve the best sampling eye for the RX and TX data, it is recommended to adjust the pad skew

delays as specified in Table 31. These values have been successfully tested on Enclustra side.

The delays can be adjusted by programming the RGMII pad skew registers of the Ethernet PHY; please refer

to the PHY datasheet for details.

PHY Register Name Register Value [binary] Delay Value

RXD0-RXD3 0111 0 ps

RX_DV 0111 0 ps

RX_CLK 01111 0 ps

TXD0-TXD3 0111 0 ps

TX_EN 0111 0 ps

GTX_CLK 11110 900 ps

Table 31: Gigabit Ethernet PHY (PS) Configuration - RGMII Delays

D-0000-445-001 44 / 64 Version 07, 25.07.2019

Loading...

Loading...