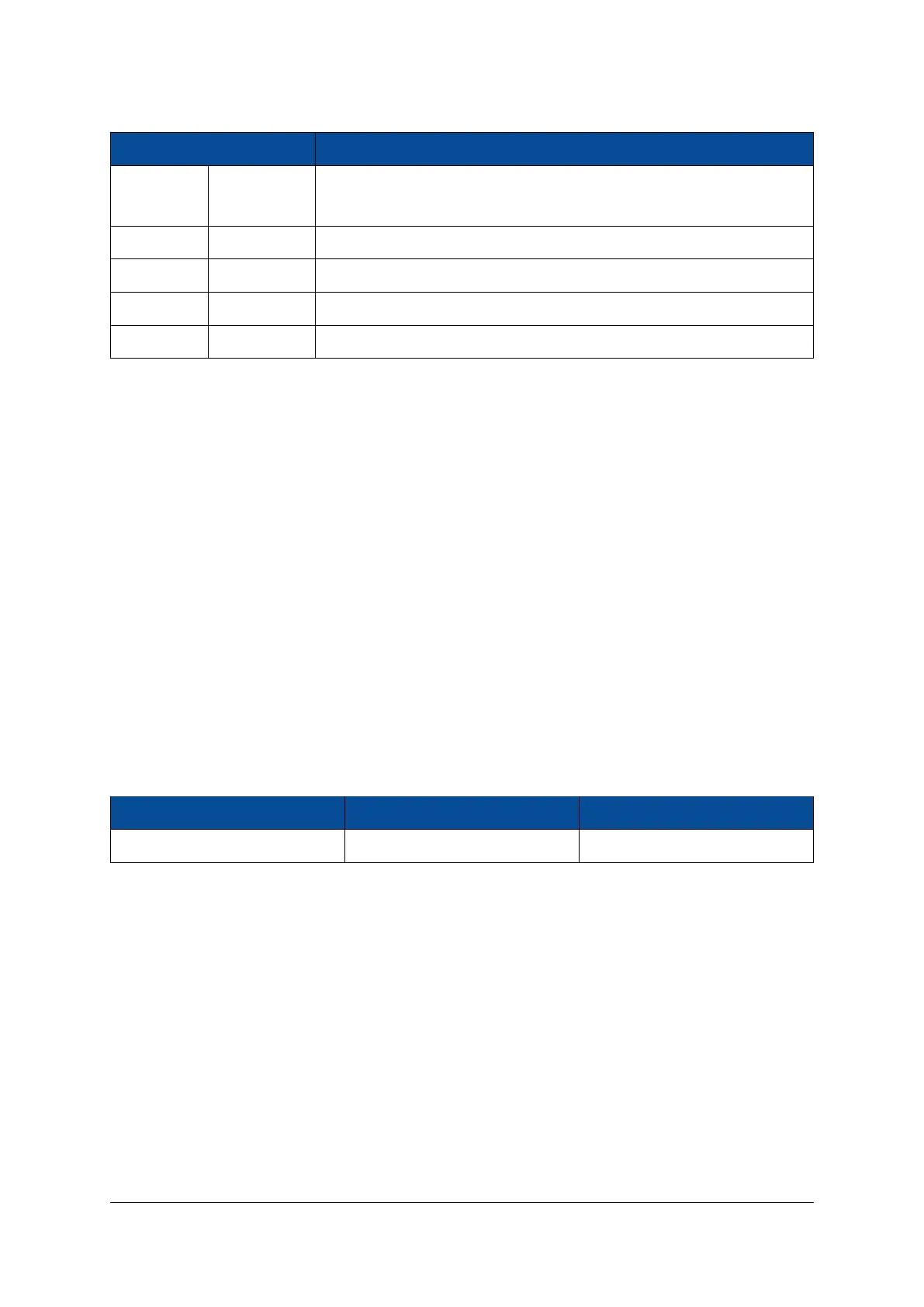

Pin Signal Value Description

MODE[3-0] 1110 RGMII mode: advertise all capabilities (10/100/1000, half/full duplex) ex-

cept 1000Base-T half duplex.

PHYAD[2-0] 011 MDIO address 3

Clk125_EN 0 125 MHz clock output disabled

LED_MODE 1 Single LED mode

LED1/LED2 1 Active-low LEDs

Table 33: Gigabit Ethernet PHY (PL) Configuration - Bootstraps

For the Ethernet PHY configuration via the MDIO interface, the MDC clock frequency must not exceed 2

MHz.

2.21.6 RGMII Delays Configuration

The Ethernet PHY (PL) is connected to the PL side of the MPSoC device, to be used in combination with a

soft MAC controller. In order to achieve the best sampling eye for the RX and TX data, it is recommended

to adjust the timing constraints of the FPGA pins and/or the pad skew delays of the Ethernet PHY. Please

refer to the Ethernet PHY datasheet for details on how to program the RGMII pad skew registers.

In the Mercury XU5 SoC module reference design the RGMII delays are set through timing constraints.

2.22 USB 2.0

Two USB 2.0 PHYs are available on the Mercury XU5 SoC module, both connected to the PS to I/O bank

502. USB PHY 0 can be configured as host or device, while USB PHY 1 can be used only as host.

2.22.1 USB PHY Type

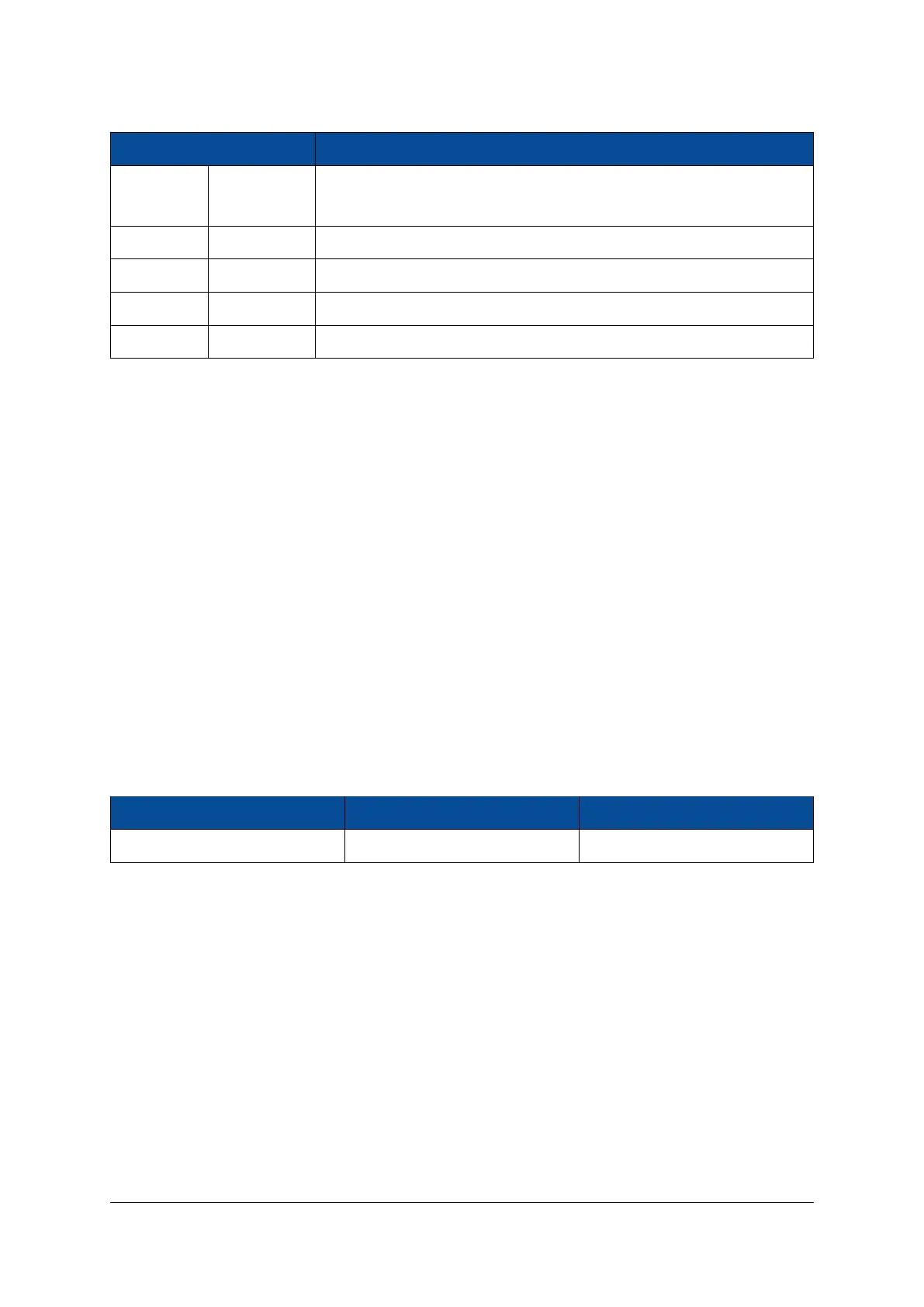

Table 34 describes the equipped USB PHYs device type on the Mercury XU5 SoC module.

PHY Type Manufacturer Type

USB3320C Microchip USB 2.0 PHY

Table 34: USB 2.0 PHY Type

2.22.2 Signal Description

The ULPI interface for the PHY 0 is connected to MIO pins 52-63, while the interface for the PHY 1 is con-

nected to MIO pins 64-75, both connected for use with the integrated USB controller.

2.23 USB 3.0

Xilinx Zynq Ultrascale+ devices feature two built-in USB 3.0 controllers and PHYs, configurable as host or

device. The PHY interface used by the USB 3.0 controller is PIPE3, supporting a 5 Gbit/sec data rate in host

or device modes. The interface of each USB 3.0 controller uses one of the PS GTR lanes.

D-0000-445-001 46 / 64 Version 07, 25.07.2019

Loading...

Loading...