3 Device Configuration

3.1 Configuration Signals

The PS of the MPSoC needs to be configured before the FPGA logic can be used. Xilinx Zynq devices need

special boot images to boot from QSPI flash, eMMC flash or SD card. For more information, please refer to

the Zynq UltraScale+ MPSoC Technical Reference Manual [19].

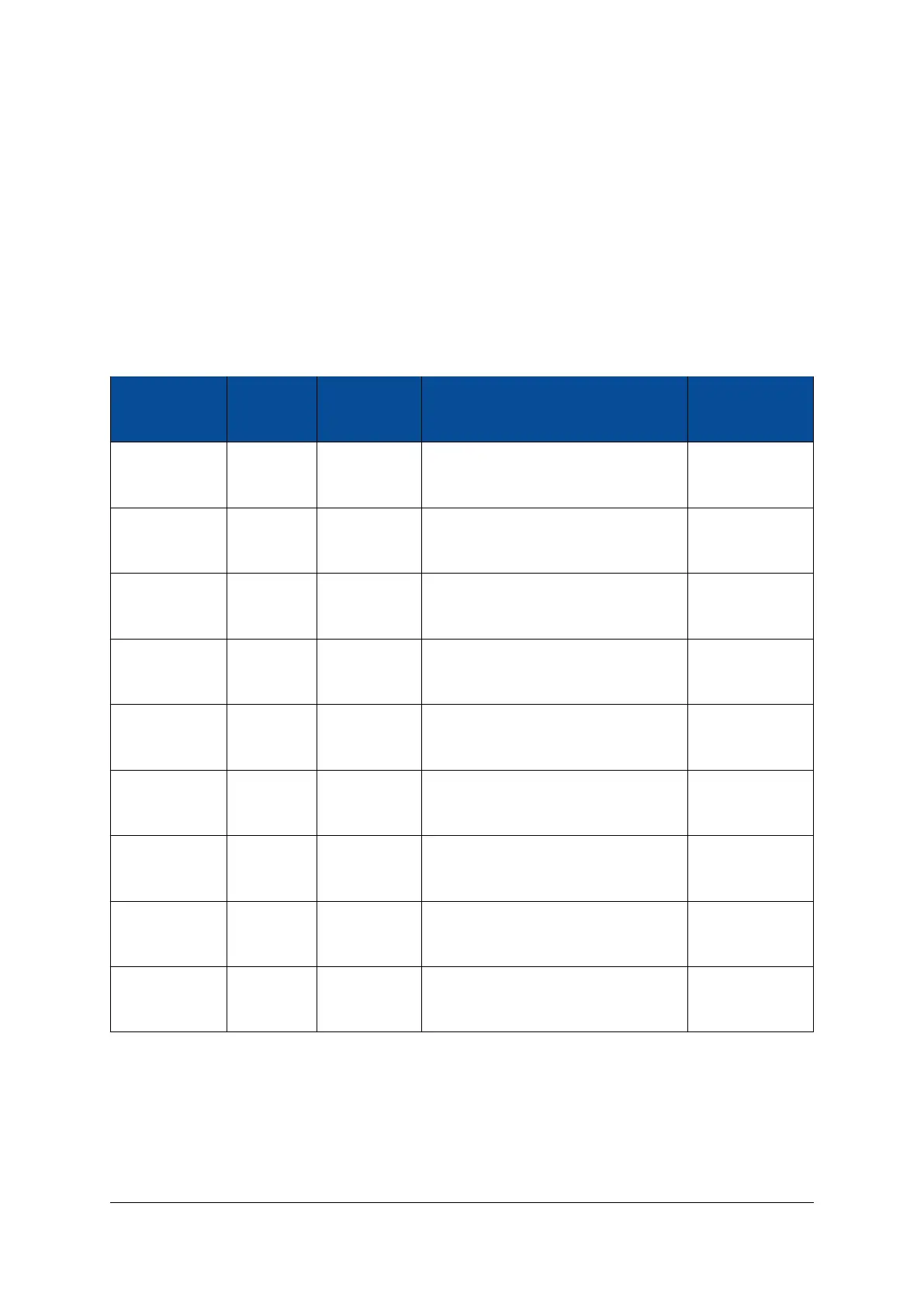

Table 36 describes the most important configuration pins and their location on the module connector. These

signals allow the MPSoC to boot from QSPI flash, eMMC flash or SD card, and can be used to program the

QSPI flash from an external master. Please refer to Section 3.11 for details.

Signal MPSoC Mod. Conn.

Name Pin Type Pin Description Comments

FLASH_CLK MIO0 A-118 SPI CLK

10 kΩ pull-up to

VCC_CFG_MIO

FLASH_DO MIO1 A-122 SPI MISO

10 kΩ pull-up to

VCC_CFG_MIO

FLASH_DI MIO4 A-114 SPI MOSI

10 kΩ pull-up to

VCC_CFG_MIO

FLASH_CS# MIO5 A-116 SPI CS#

10 kΩ pull-up to

VCC_CFG_MIO

PS_DONE PS_DONE A-130 MPSoC device configuration done

1 kΩ pull-up to

VCC_CFG_MIO

PS_POR# PS_POR_B A-132 MPSoC power-on reset

10 kΩ pull-up to

VCC_CFG_MIO

PS_SRST# PS_SRST_B A-124 MPSoC system reset

10 kΩ pull-up to

VCC_CFG_MIO

BOOT_MODE0 - A-126 Boot mode selection

10 kΩ pull-up to

VCC_CFG_MIO

BOOT_MODE1 - A-112 Boot mode selection

10 kΩ pull-up to

VCC_CFG_MIO

Table 36: MPSoC Configuration Pins

D-0000-445-001 49 / 64 Version 07, 25.07.2019

Loading...

Loading...