For details on the PUDC signal please refer to the Zynq UltraScale+ MPSoC Technical Reference Manual

[19].

3.3 Power-on Reset Delay Override

The power-on reset delay override MPSoC signal (POR_OVERRIDE) is pulled to GND on the module, setting

the PL power-on delay time to the default standard time.

If the application requires faster PL power-on delay time, this can be achieved by removing R203 component

and by mounting R213.

Figure 16 illustrates the configuration of the POR_OVERRIDE signal. Figure 17 indicates the location of the

pull-up/pull-down resistors on the module PCB - middle right part on the bottom view drawing.

For details on the POR_OVERRIDE signal please refer to the Zynq UltraScale+ MPSoC Technical Reference

Manual [19].

3.4 Boot Mode

The boot mode can be selected via two signals available on the module connector.

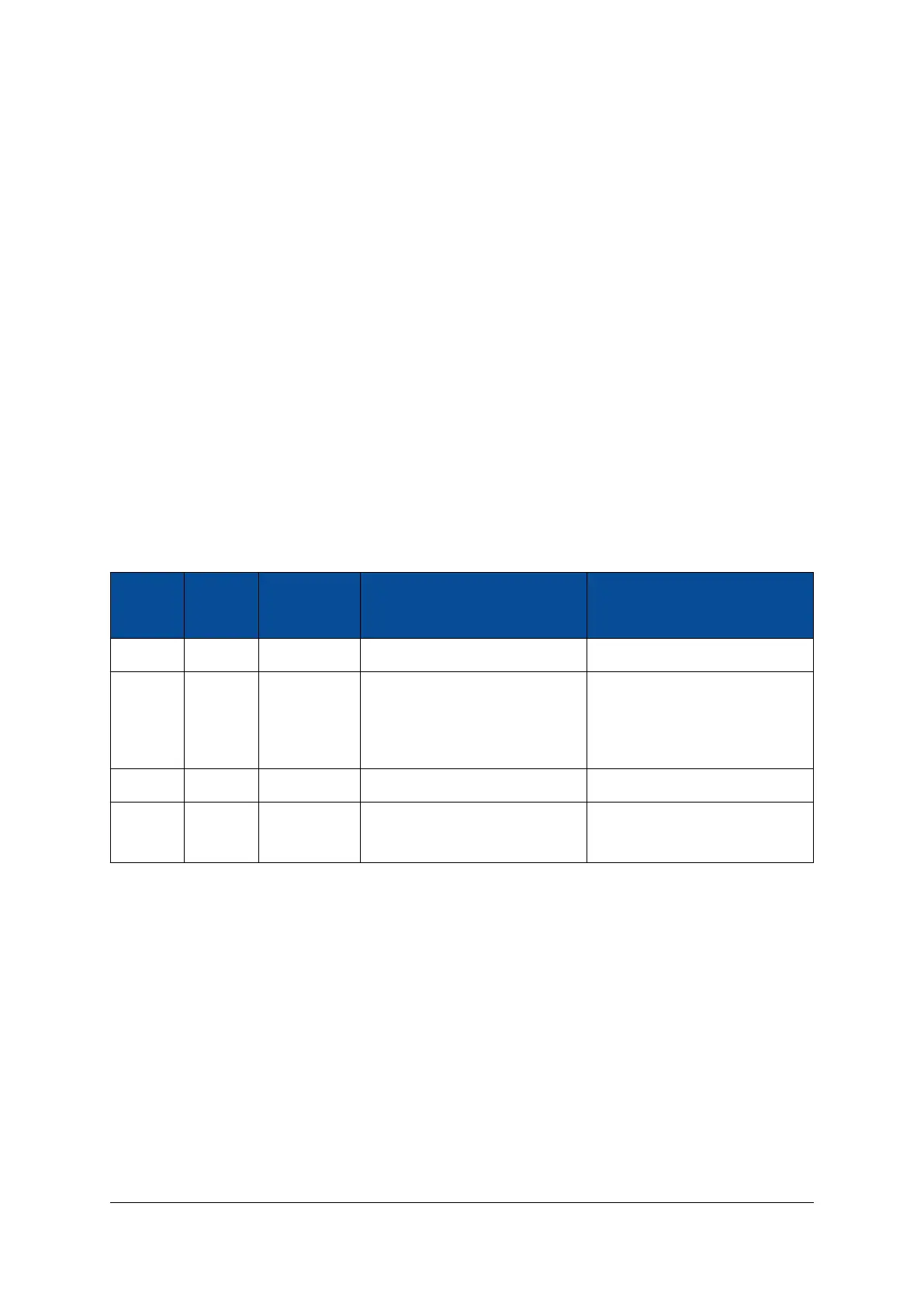

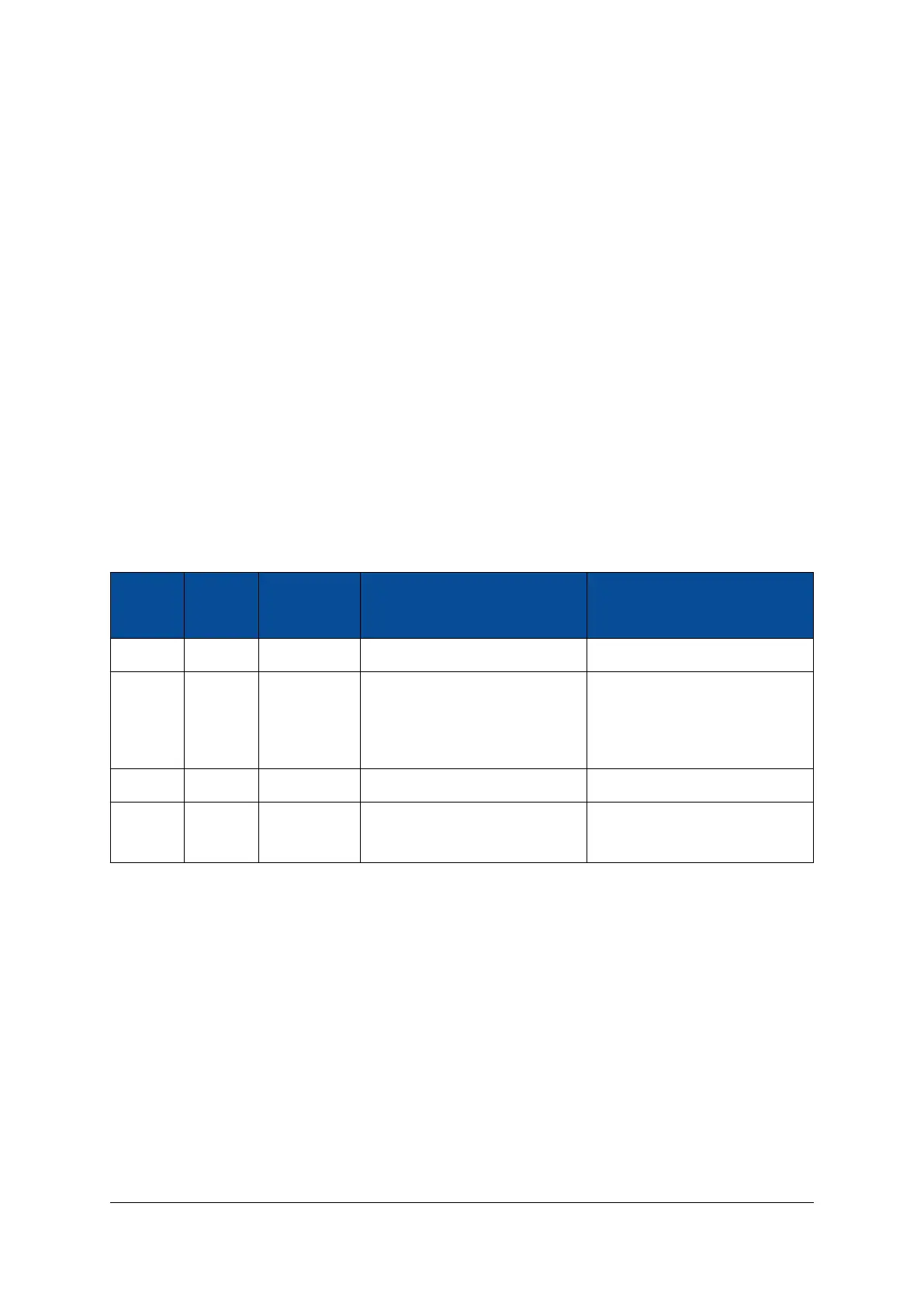

Table 37 describes the available boot modes on the Mercury XU5 SoC module.

BOOT BOOT Mode Description Remarks

MODE1 MODE0 Straps [3:0]

0 0 0110 Boot from eMMC flash -

0 1 1110 Boot from SD card (with an ex-

ternal SD 3.0 compliant level

shifter; only available when

VCC_CFG_MIO is 1.8 V)

Not supported (may be sup-

ported in the future)

1 0 0010 Boot from QSPI flash -

1 1 0101 Boot from SD card (default

mode)

-

Table 37: Boot Modes

3.5 JTAG

The Zynq Ultrascale+ devices include two separate JTAG controllers: the Zynq Ultrascale+ TAP and the ARM

DAP. The first one uses the PS dedicated JTAG pins and has access to both PS and PL and the second one

uses the PS PJTAG pins and is used for loading programs, system test, and PS debug.

Details on JTAG and on system test and debug are available in the Zynq UltraScale+ MPSoC Technical Ref-

erence Manual [19].

Certain Xilinx tool versions support QSPI flash programming via JTAG only when JTAG boot mode is used

(unavailable on the Mercury XU5 SoC module). Alternatively, the QSPI flash can be programmed in u-boot

or Linux by the SPI controller in the PS or from an SPI external master.

D-0000-445-001 51 / 64 Version 07, 25.07.2019

Loading...

Loading...