2.21 Gigabit Ethernet (PL)

2.21.1 Ethernet PHY Type

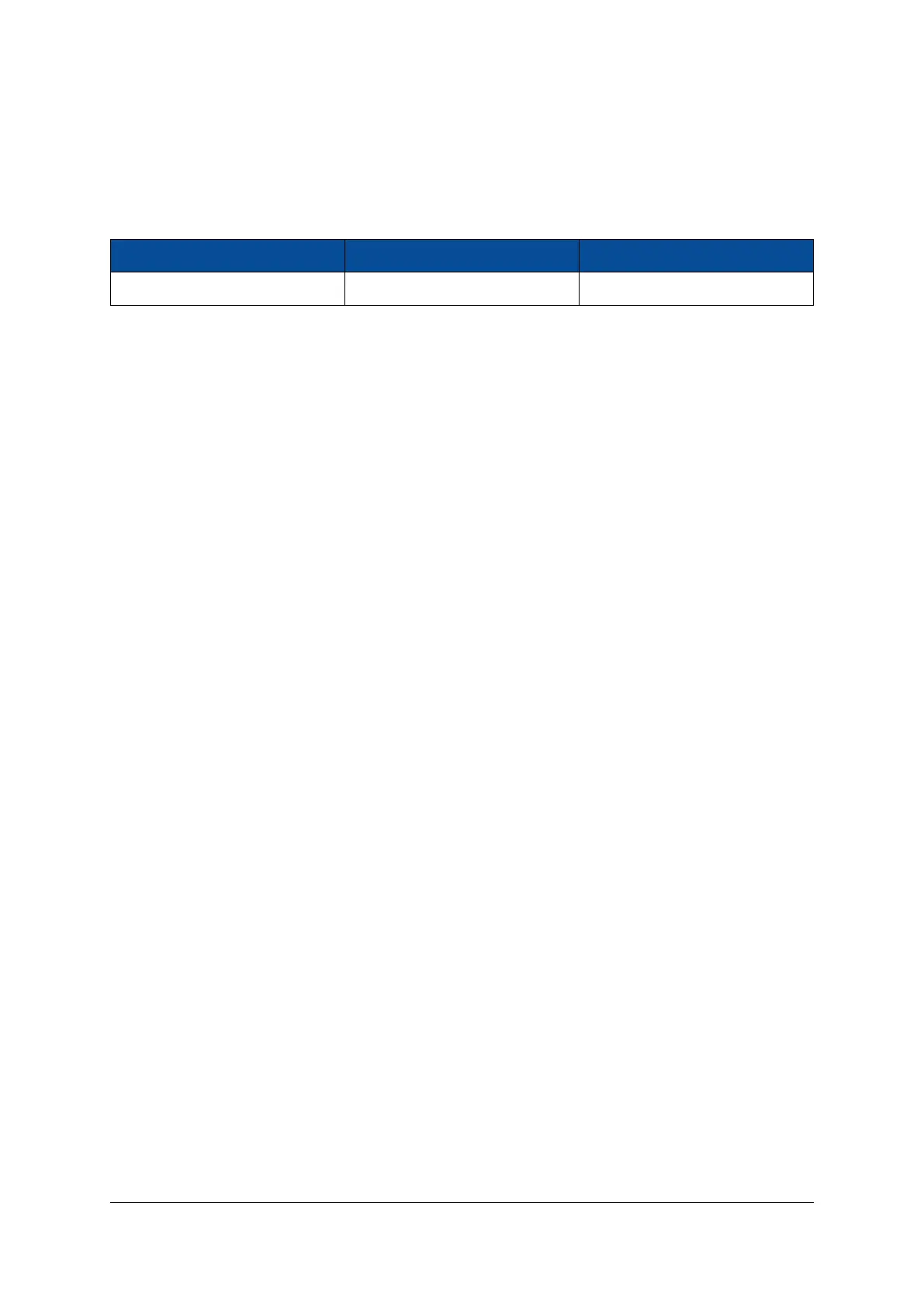

Table 32 describes the equipped Ethernet PHY (PL) device type on the Mercury XU5 SoC module.

PHY Type Manufacturer Type

KSZ9031RNX Microchip (Micrel) 10/100/1000 Mbit

Table 32: Gigabit Ethernet PHY (PL) Type

2.21.2 Signal Description

Ethernet PHY 1 is connected to FPGA bank E (25 for ZU2/ZU3 and 45 for ZU4/ZU5), for usage with a soft

Ethernet MAC IP core providing RGMII interface for communication with the PHY.

Alternatively, the Ethernet MAC from the PS can be used and mapped to EMIO pins. An GMII to RGMII

converter must be used to convert the bus to the appropriate interface standard. Please note that the Xilinx

GMII to RGMII converter cannot be used on the Mercury XU5 SoC module because this IP core includes I/O

delay macros that are not supported in HD I/O banks (where the Ethernet pins are mapped).

The reset pin of the Ethernet PHY has a pull-down resistor and needs to be driven high to release the PHY

from reset. The reset pin is connected to FPGA pin B10 from bank E (25 for ZU2/ZU3 and 45 for ZU4/ZU5).

The interrupt output of the Ethernet PHY is connected to FPGA pin C11 from the same bank.

2.21.3 External Connectivity

The Ethernet signal lines can be connected directly to the magnetics. Please refer to the Enclustra Module

Pin Connection Guidelines [11] for details regarding the connection of Ethernet signals.

2.21.4 MDIO Address

The MDIO address assigned to PHY 1 is 3, and the PHY can be configured via FPGA pins A10 and B11 from

bank E (25 for ZU2/ZU3 and 45 for ZU4/ZU5).

2.21.5 PHY Configuration

The configuration of the Ethernet PHY is bootstrapped when the PHYs are released from reset. Make sure all

I/Os on the RGMII interface are initialized and all pull-up or pull-down resistors are disabled at that moment.

The bootstrap options of the Ethernet PHYs are set as indicated in Table 33.

D-0000-445-001 45 / 64 Version 07, 25.07.2019

Loading...

Loading...