Chapter 4. API Guides

• If the Core Dump feature is enabled, then the system state (task stacks and registers) will be dumped to either

Flash or UART, for later analysis.

• If CONFIG_ESP_PANIC_HANDLER_IRAM is disabled (disabled by default), the panic handler code is placed

in flash memory, not IRAM. This means that if ESP-IDF crashes while flash cache is disabled, the panic handler

will automatically re-enable flash cache before running GDB Stub or Core Dump. This adds some minor risk,

if the flash cache status is also corrupted during the crash.

If this option is enabled, the panic handler code (including required UART functions) is placed in IRAM, and

hence will decrease the usable memory space in SRAM. But this may be necessary to debug some complex

issues with crashes while flash cache is disabled (for example, when writing to SPI flash) or when flash cache

is corrupted when an exception is triggered.

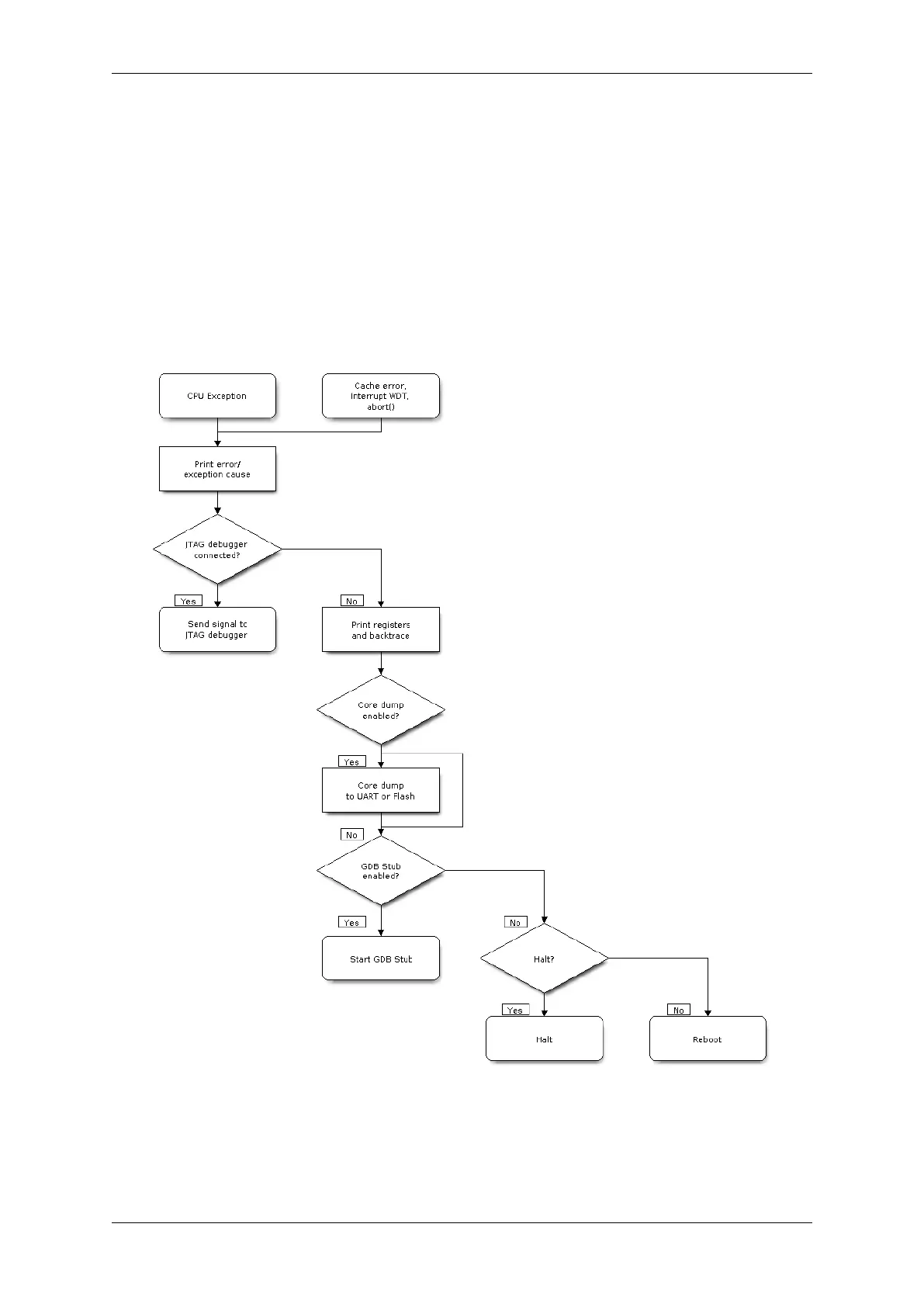

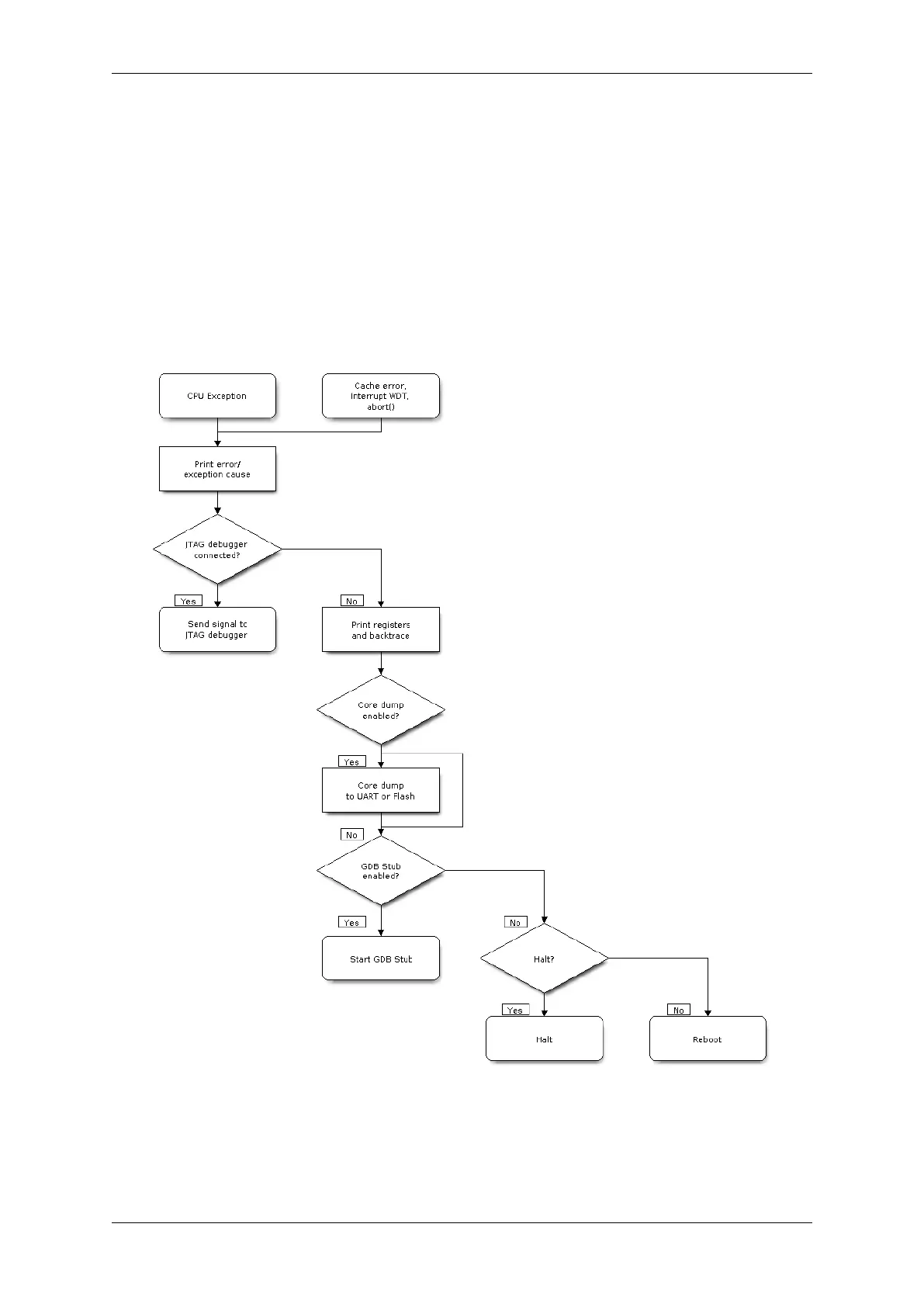

The following diagram illustrates the panic handler behavior:

Fig. 19: Panic Handler Flowchart (click to enlarge)

Espressif Systems 1336

Submit Document Feedback

Release v4.4

Loading...

Loading...