Chapter 2. API Reference

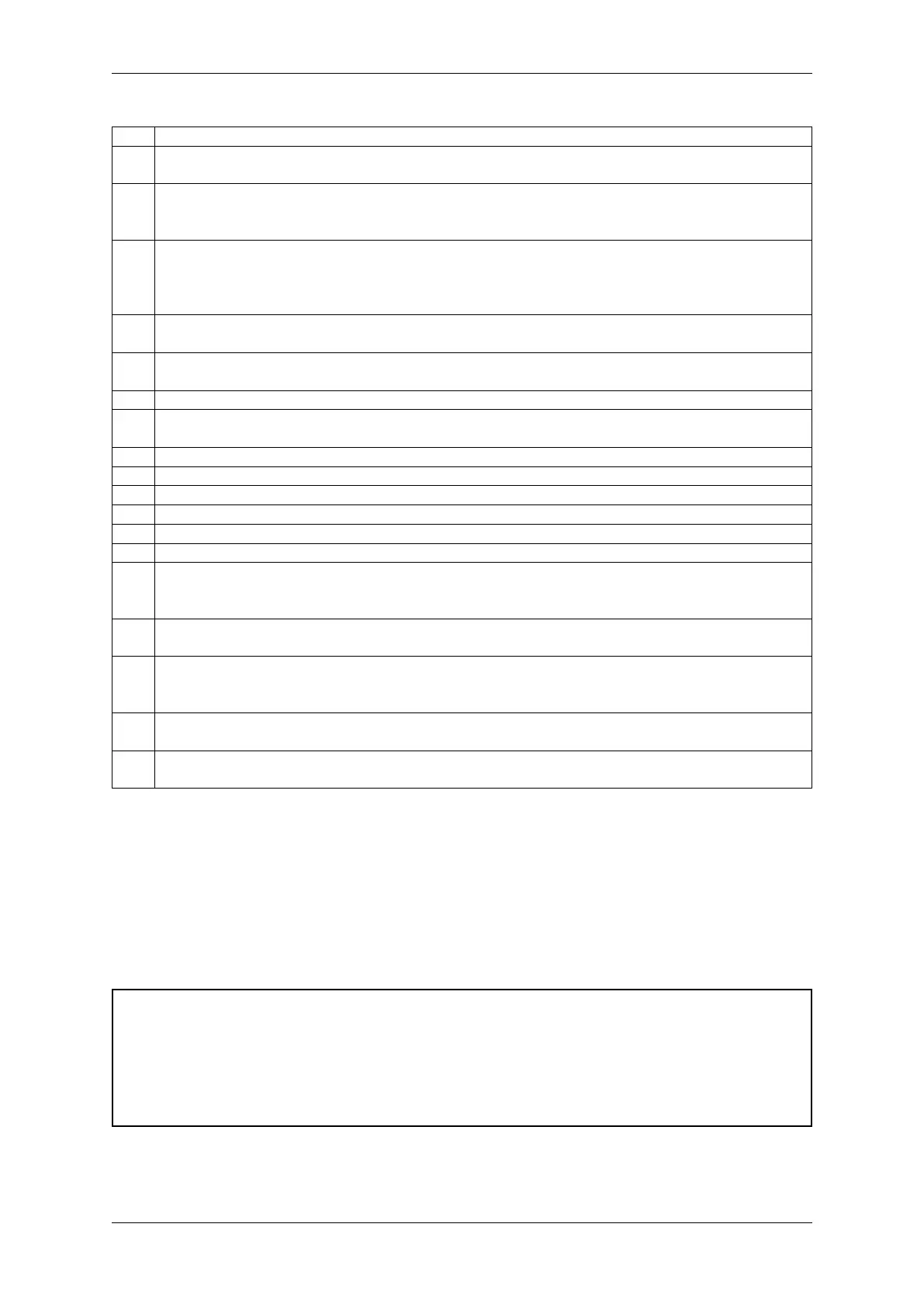

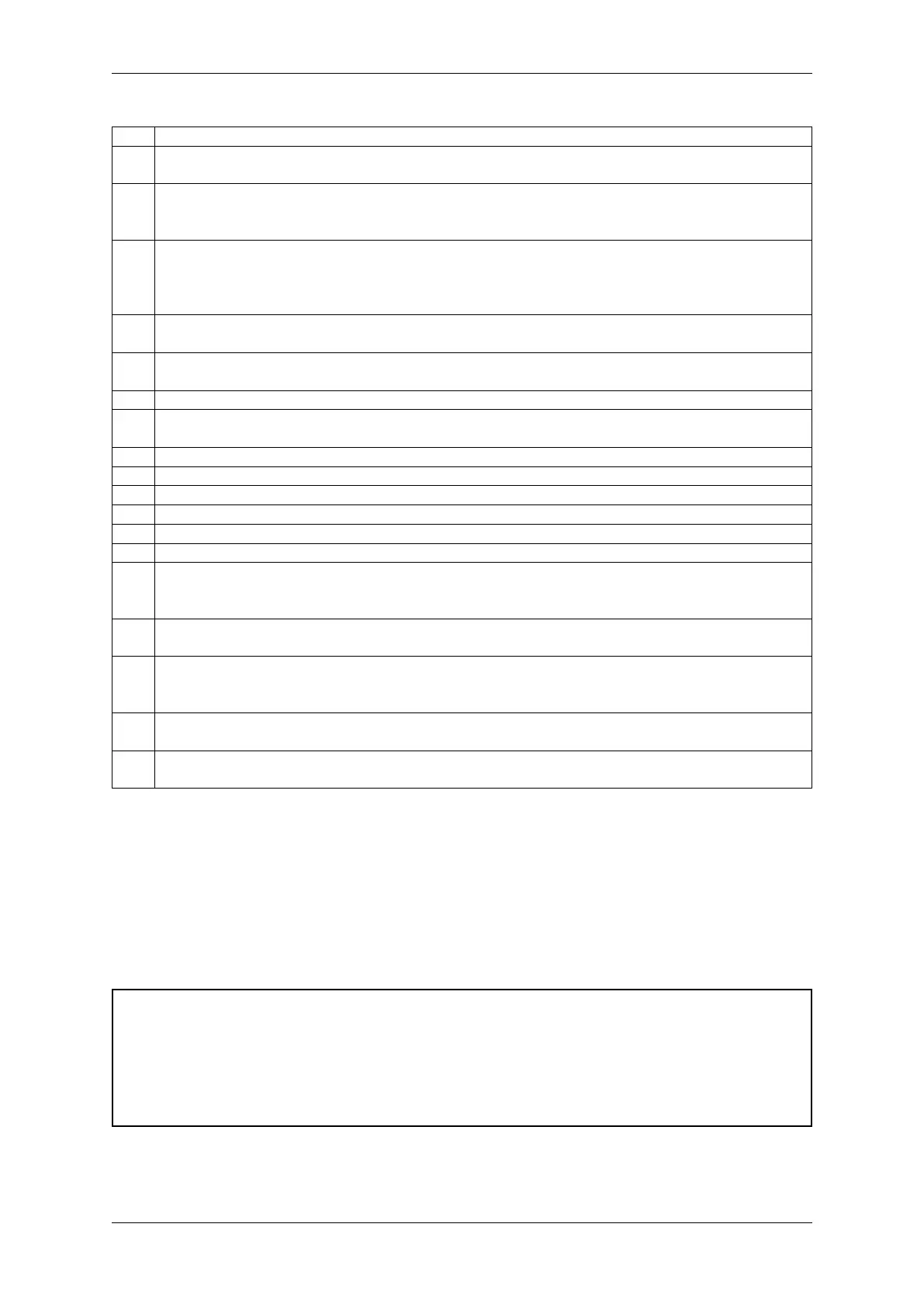

Term Definition

Host The SPI controller peripheral inside ESP32-S2 that initiates SPI transmissions over the bus, and acts as an

SPI Master.

De-

vice

SPI slave device. An SPI bus may be connected to one or more Devices. Each Device shares the MOSI,

MISO and SCLK signals but is only active on the bus when the Host asserts the Device’s individual CS

line.

Bus A signal bus, common to all Devices connected to one Host. In general, a bus includes the following lines:

MISO, MOSI, SCLK, one or more CS lines, and, optionally, QUADWP and QUADHD. So Devices are

connected to the same lines, with the exception that each Device has its own CS line. Several Devices can

also share one CS line if connected in the daisy-chain manner.

MOSIMaster Out, Slave In, a.k.a. D. Data transmission from a Host to Device. Also data0 signal in Octal/OPI

mode.

MISOMaster In, Slave Out, a.k.a. Q. Data transmission from a Device to Host. Also data1 signal in Octal/OPI

mode.

SCLKSerial Clock. Oscillating signal generated by a Host that keeps the transmission of data bits in sync.

CS Chip Select. Allows a Host to select individual Device(s) connected to the bus in order to send or receive

data.

QUADWPWrite Protect signal. Used for 4-bit (qio/qout) transactions. Also for data2 signal in Octal/OPI mode.

QUADHDHold signal. Used for 4-bit (qio/qout) transactions. Also for data3 signal in Octal/OPI mode.

DATA4Data4 signal in Octal/OPI mode.

DATA5Data5 signal in Octal/OPI mode.

DATA6Data6 signal in Octal/OPI mode.

DATA7Data7 signal in Octal/OPI mode.

As-

ser-

tion

The action of activating a line.

De-

assertion

The action of returning the line back to inactive (back to idle) status.

Trans-

ac-

tion

One instance of a Host asserting a CS line, transferring data to and from a Device, and de-asserting the CS

line. Transactions are atomic, which means they can never be interrupted by another transaction.

Launch

edge

Edge of the clock at which the source register launches the signal onto the line.

Latch

edge

Edge of the clock at which the destination register latches in the signal.

Driver Features

The SPI master driver governs communications of Hosts with Devices. The driver supports the following features:

• Multi-threaded environments

• Transparent handling of DMA transfers while reading and writing data

• Automatic time-division multiplexing of data coming from different Devices on the same signal bus, see SPI

Bus Lock.

Warning: The SPI master driver has the concept of multiple Devices connected to a single bus (sharing a

single ESP32-S2 SPI peripheral). As long as each Device is accessed by only one task, the driver is thread safe.

However, if multiple tasks try to access the same SPI Device, the driver is not thread-safe. In this case, it is

recommended to either:

• Refactor your application so that each SPI peripheral is only accessed by a single task at a time.

• Add a mutex lock around the shared Device using xSemaphoreCreateMutex.

SPI Features

Espressif Systems 365

Submit Document Feedback

Release v4.4

Loading...

Loading...