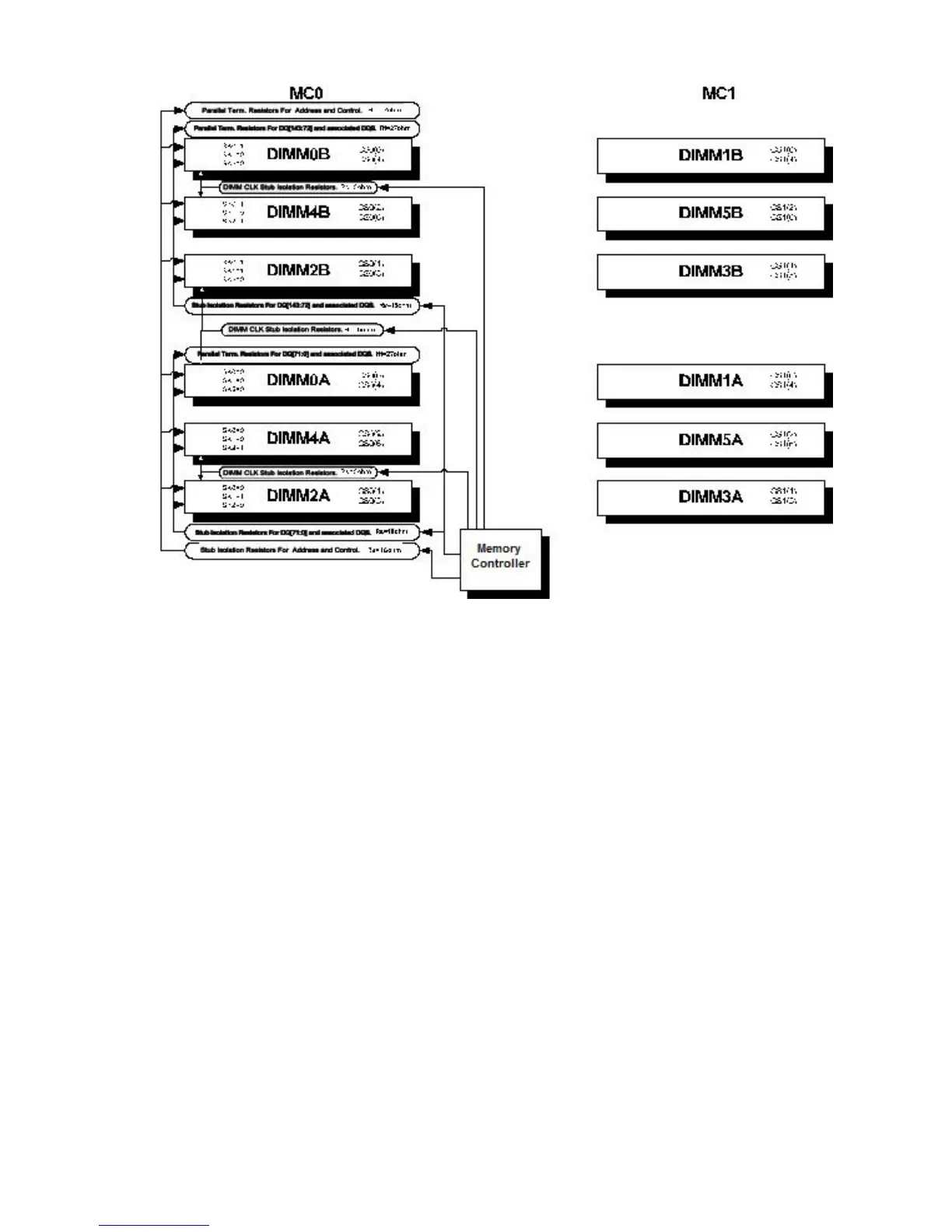

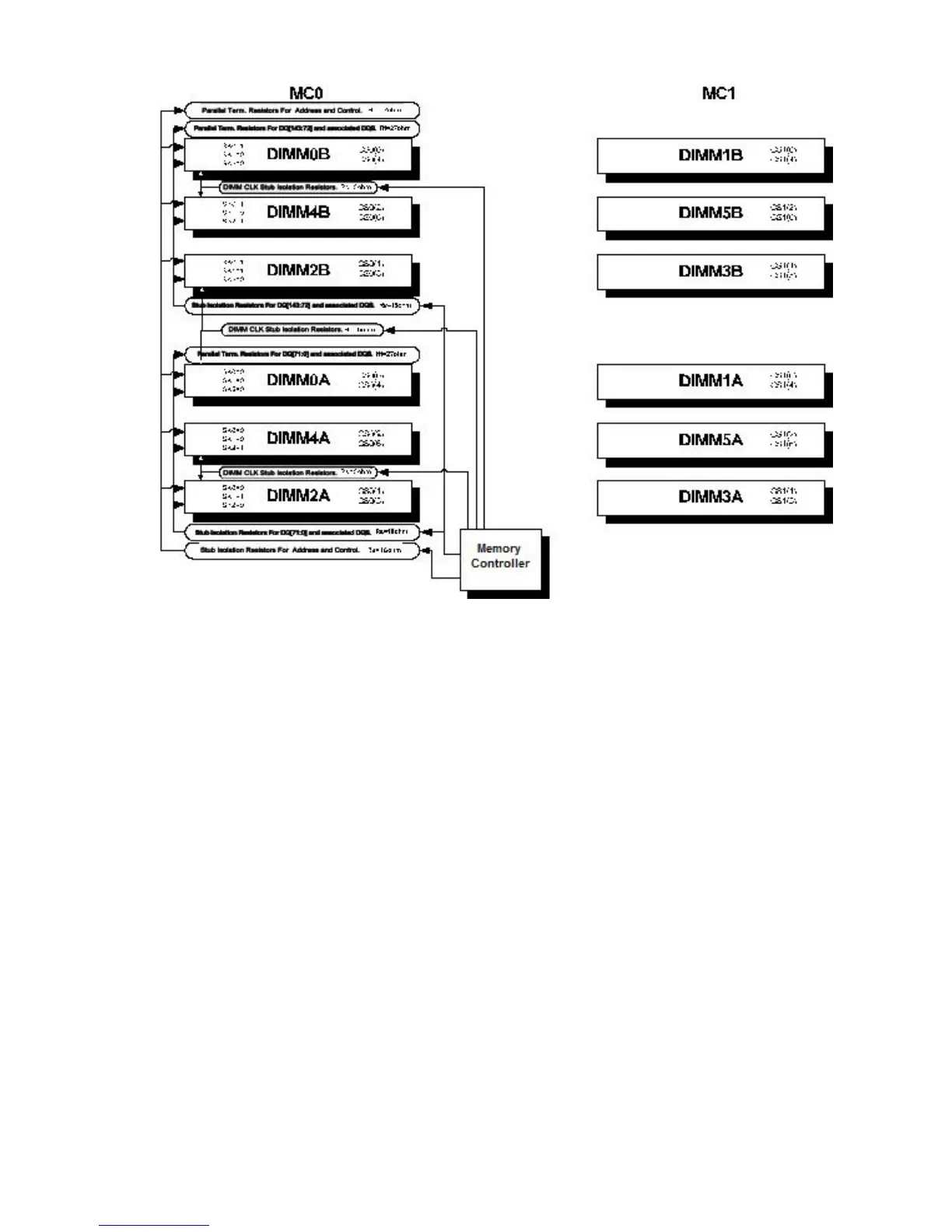

Figure 1-6 Memory Block Diagram

Memory Architecture

The I/O ASIC memory interface supports two DDR cells, each of which is 144 data bits wide.

The memory subsystem physical design uses a comb-filter termination scheme for both the data

and address/control buses. This part of the topology is similar to other DDR designs in the

computer industry. Clocks are distributed directly from the I/O ASIC; each clock pair drives two

DIMMs.

Memory data is protected by ECC. Eight ECC bits per DIMM protect 64 bits of data. The use of

ECC enables correction of single-bit errors, and detection of multi-bit errors. Only DIMMs with

ECC are qualified or supported.

DIMMs

The memory subsystem only supports Double Data Rate Synchronous Dynamic Random Access

Memory (DDR SDRAM) technology utilizing industry-standard PC-1600 type DDR SDRAM

DIMMs, 1.2" tall. This is currently being used by high-volume products. The DIMMs use a 184-pin

JEDEC standard connector.

DIMMs are loaded in groups of four, known as a rank or quad (except for 256 MB DIMMs, which

is loaded in pairs). All four DIMMs in a rank or quad must be the same size. The following

information summarizes the memory solutions.

Memory Array Capacities

Table 1-2 lists the memory array capacities for the server.

26 Overview

Loading...

Loading...