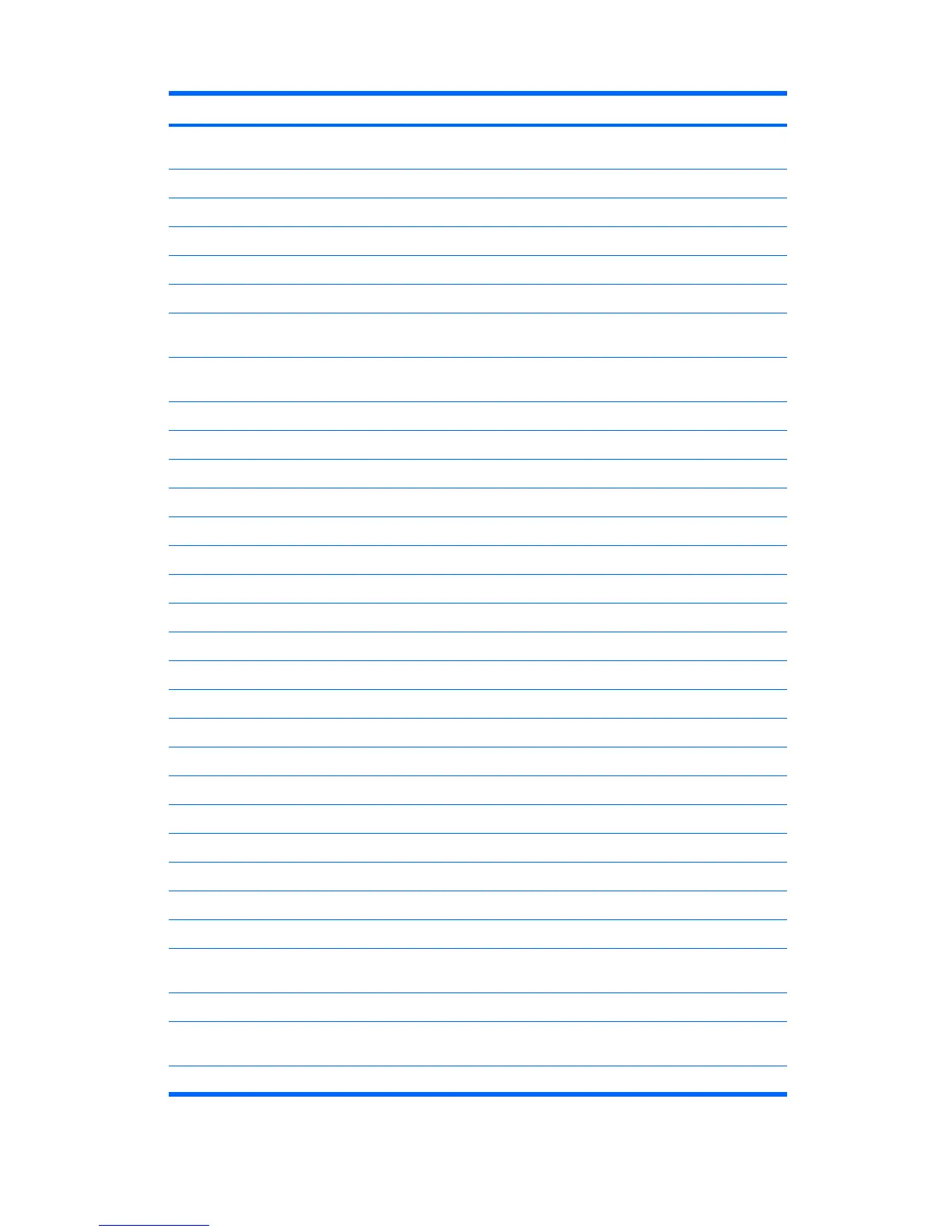

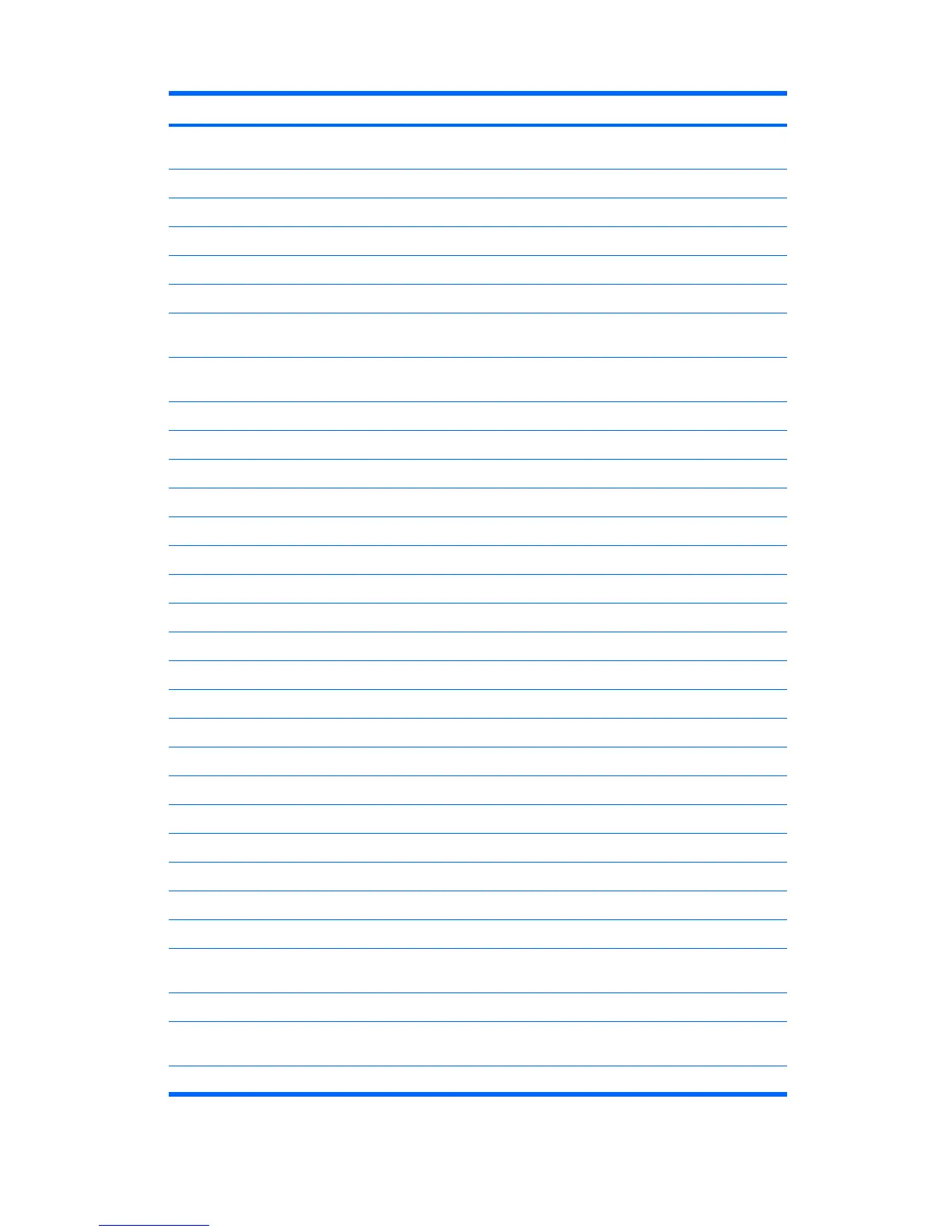

Bus# Dev# Fn# Device#

0 9 0 Advanced memory buffer memory-mapped registers (visible via

JTAG/SMBus only)

0 16 0 FSB controller, interrupt and system address registers

0 16 1 Address mapping, memory control, error logs

0 16 2 FSB error registers

0 17 0 Coherency engine and data manager registers

0 19 0 Debug and miscellaneous registers

0 21 0 FBD branch 0 memory map, error flag/mask, and channel control

registers

0 22 0 FBD branch 1 memory map, error flag/mask, and channel control

registers

0 27 0 High definition audio controller

0 28 0 Port 1 PCI Express x4 to slot 2 (secondary bus: 8)

0 28 1 (PCI Express port 2, hidden)

0 28 2 (PCI Express port 3, hidden)

0 28 3 (PCI Express port 4, hidden)

0 29 0 USB UHCI controller #1

0 29 1 USB UHCI controller #2

0 29 2 USB UHCI controller #3

0 29 3 USB UHCI controller #4

0 29 7 USB 2.0 EHCI controller

0 30 0 PCI to PCI bridge (secondary bus: 1, to slot 5 and 6)

0 30 2 AC97 audio controller

0 31 0 LPC controller

0 31 1 IDE controller

0 31 2 SATA controller

0 31 3 SMBus controller

1 4 x Slot 5 (PCI)

1 9 x Slot 6 (PCI)

M(16) 0 0 PCI Express upstream port (secondary bus: P)

P(30) 0 0 PCI Express downstream port E1 (secondary bus: Q) to slot 4

(x8')

P(30) 1 0 PCI Express downstream port E2 (secondary bus: NIC) to LOM

P(30) 2 0 PCI Express downstream port E3 (secondary bus: S, internal, not

used)

31 0 0 Broadcom LOM (NIC)

Table H-1 PCI device list (continued)

ENWW PCI bus layout and device list 197

Loading...

Loading...