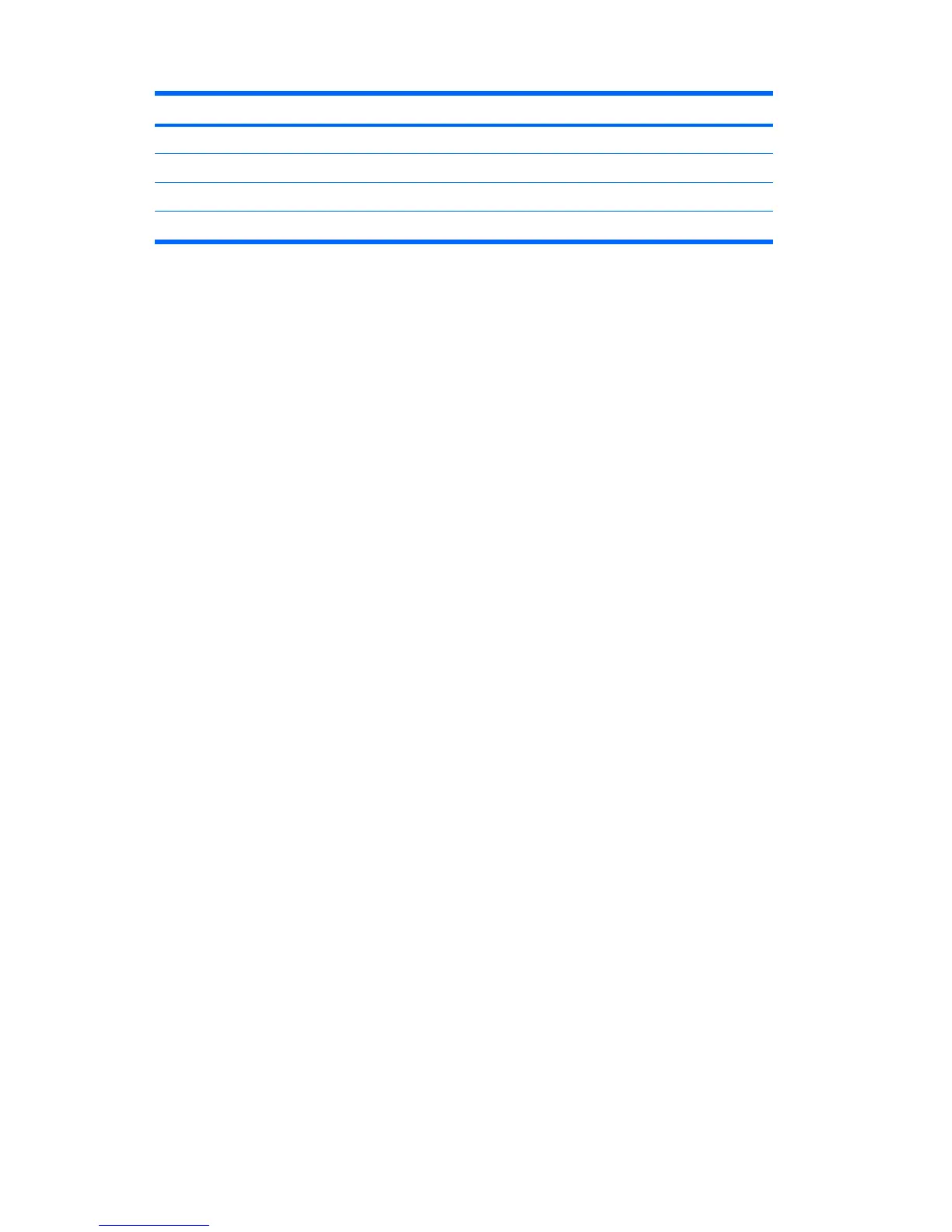

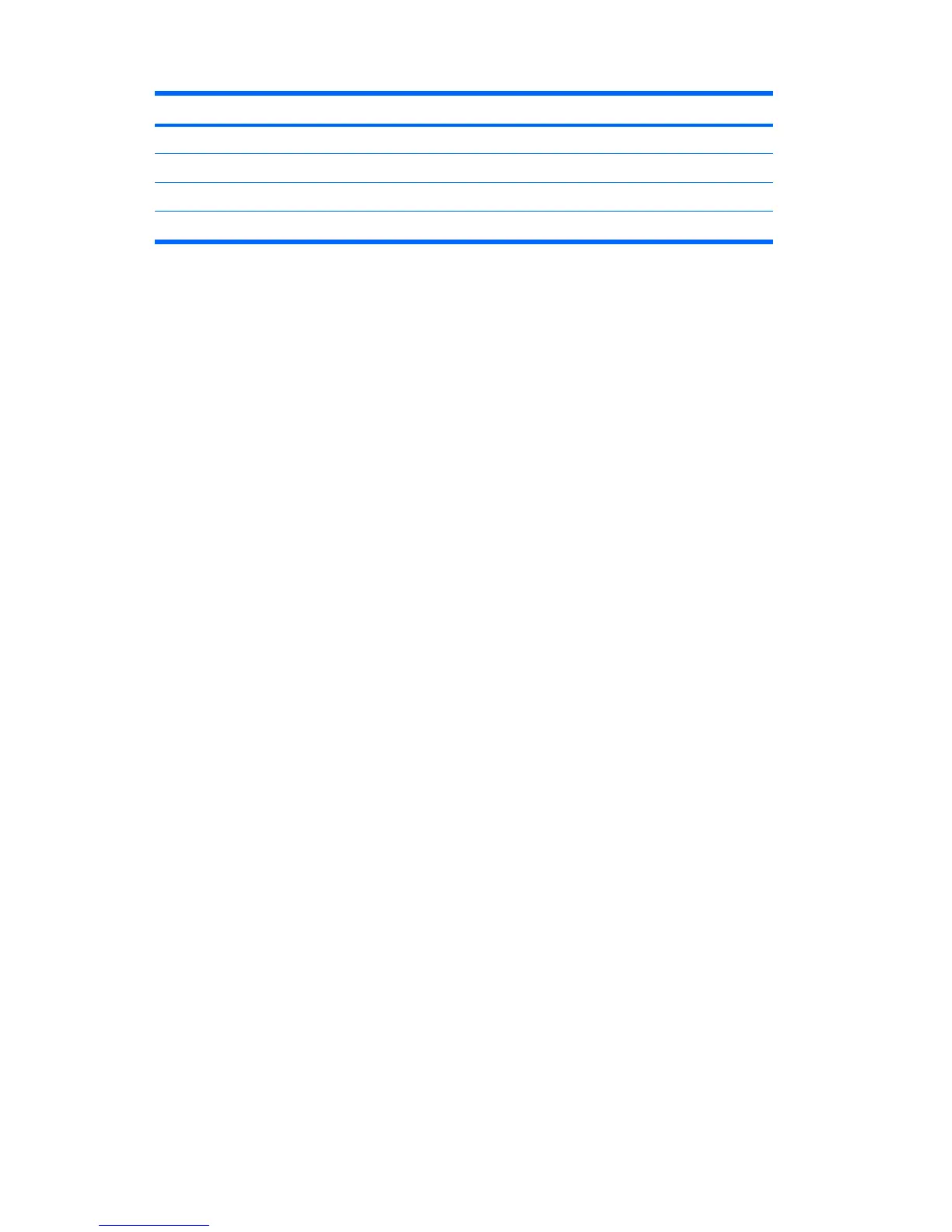

Bus# Dev# Fn# Device#

32 0 x Slot 4 (PCI Express x4 (x8') behind ESB2 P:0:0)

64 0 x Slot 1 (PCI Express x16 behind MCH 0:4:0)

96 0 x Slot 3 (PCI Express x4 (x16') behind MCH 0:3:0_

128 0 x Slot 2 PCI Express x4, (behind MCH 0:28:0)

Table H-1 PCI device list (continued)

198 Appendix H Appendix H — PCI bus layout ENWW

Loading...

Loading...