Shenzhen Hpmont Technology Co., Ltd. Appendix B Communication Protocol

HD3N Series User Manual V1.1 - 151 -

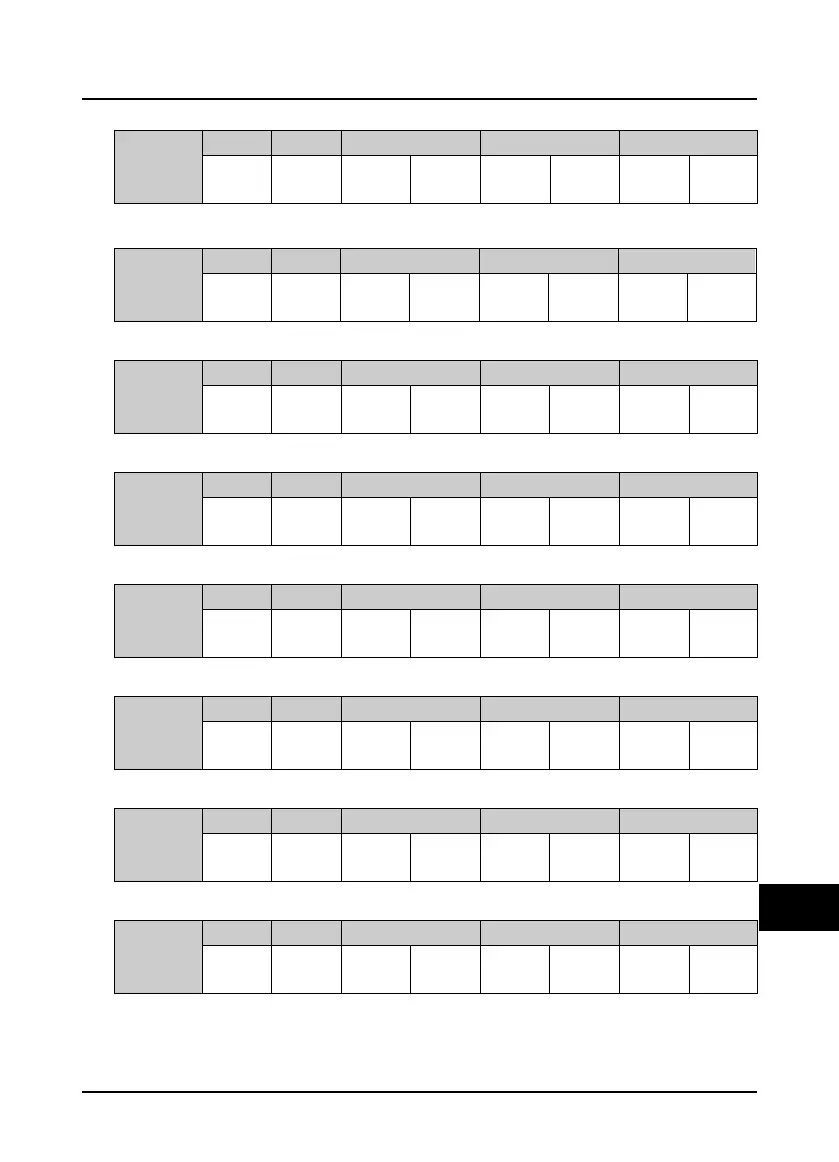

3. To write setting frequency of address 2 (F00.13 = 45.00Hz)

Command /

Response

Frame

Address Code Register address Register content Checksum

0x02 0x06 0x00 0x0D 0x11 0x94 0x15 0xC5

4. F00.10 = 2, write setting running frequency of address 2 = 45.00Hz, register content 0x11,0x94

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x01 0x11 0x94 0xDB 0x7E

5. F00.11 = 2, address 2 is reverse

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x10 0x03 0xCA 0x80

6. F00.11 = 2, address 2 decelerates to stop

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x10 0x04 0x8B 0x42

7. F00.11 = 2, address 2 emergency stops

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x10 0x08 0x8B 0x47

8. F00.11 = 2, address 2 coasts to stop

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x10 0x10 0x8B 0x4D

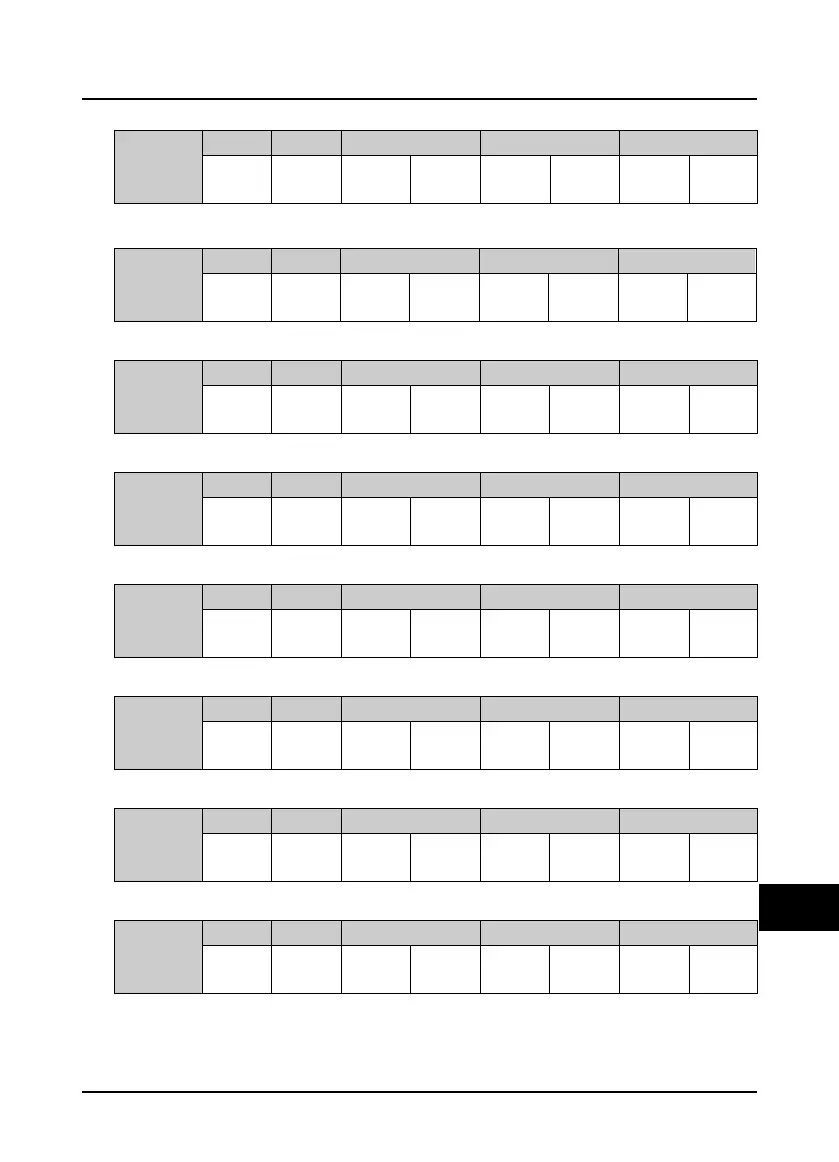

9. Address 2 has external fault

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x10 0x20 0x8B 0x59

10. Address 2 fault reset

Command /

Response

Frame

Add. Code Register address Register content Checksum

0x02 0x06 0x32 0x00 0x11 0x00 0x8B 0x11

Loading...

Loading...