Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Memory Map

Page 28 of 115

750FXebm_ch3.fm

June 10, 2003

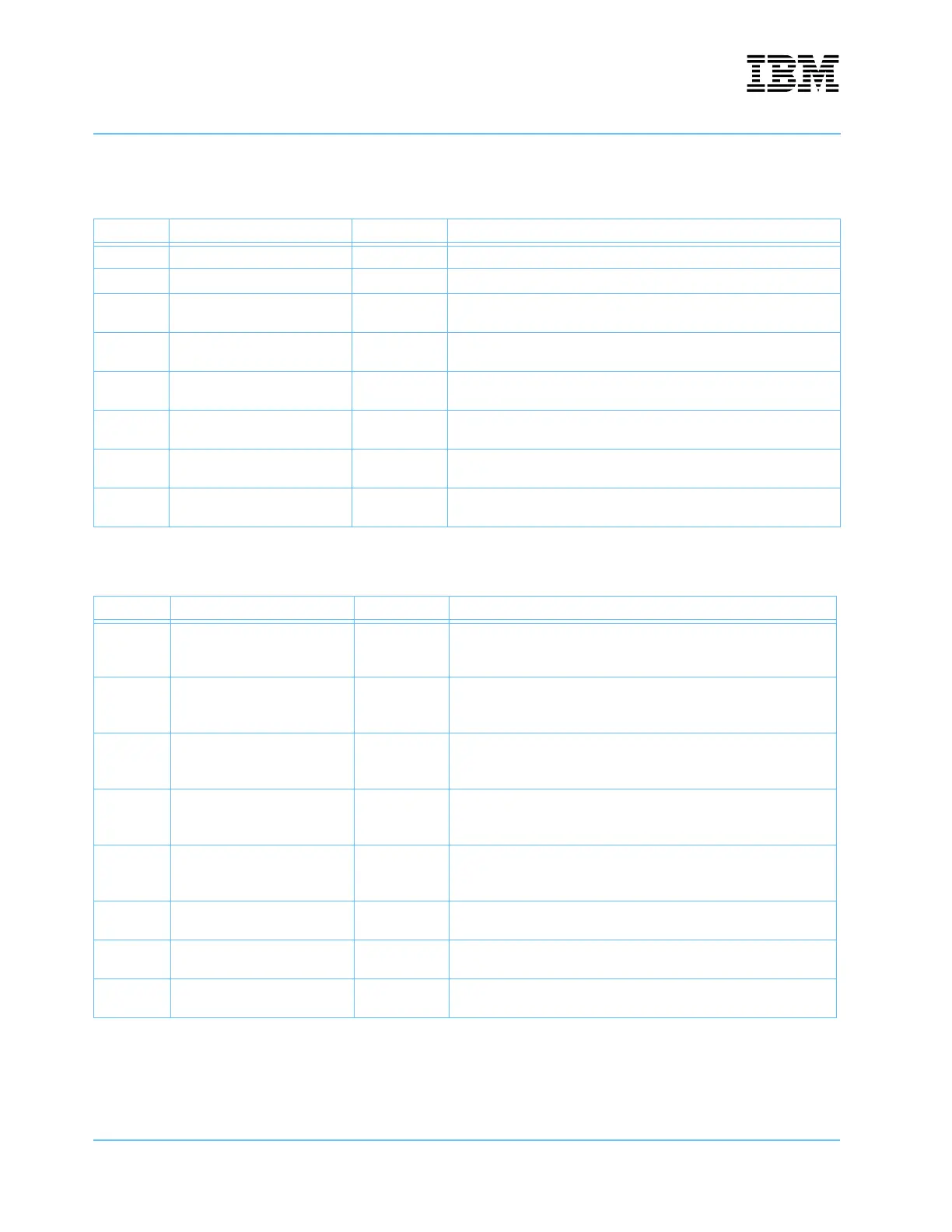

Table 3-3. Register1

Note: This register should be written before reading in order to latch the most current status. Any value can be written to the register.

Bit Name R/W Description

0 (msb) na na Unused

1 na na Unused

2 ATX or PCI Power R

0 = Using an ATX power supply

1 = Power obtained from a PCI slot

3 Spare Switch B R

0 = U35 Switch 8 is ON

1 = U35 Switch 8 is OFF

4 Spare Switch A R

0 = U30 Switch 8 is ON

1 = U30 Switch 8 is OFF

5 PCI Adapter/Host select R

0 = PCI Host mode U24 Switch 6 is ON

1 = PCI Adapter mode U24 Switch 6 is OFF

6 8-bit Flash/SRAM swap select R

0 = 8-bit Flash is at a higher address in memory, U24 Switch 6 is ON

1 = 8-bit SRAM is at a higher address in memory, U24 Switch 6 is ON

7 (lsb) BootFlash select R

0 = Booted from 8-bit flash or SRAM U17 Switch 6 is ON

1 = Booted from 32-bit flash U17 Switch 6 is OFF

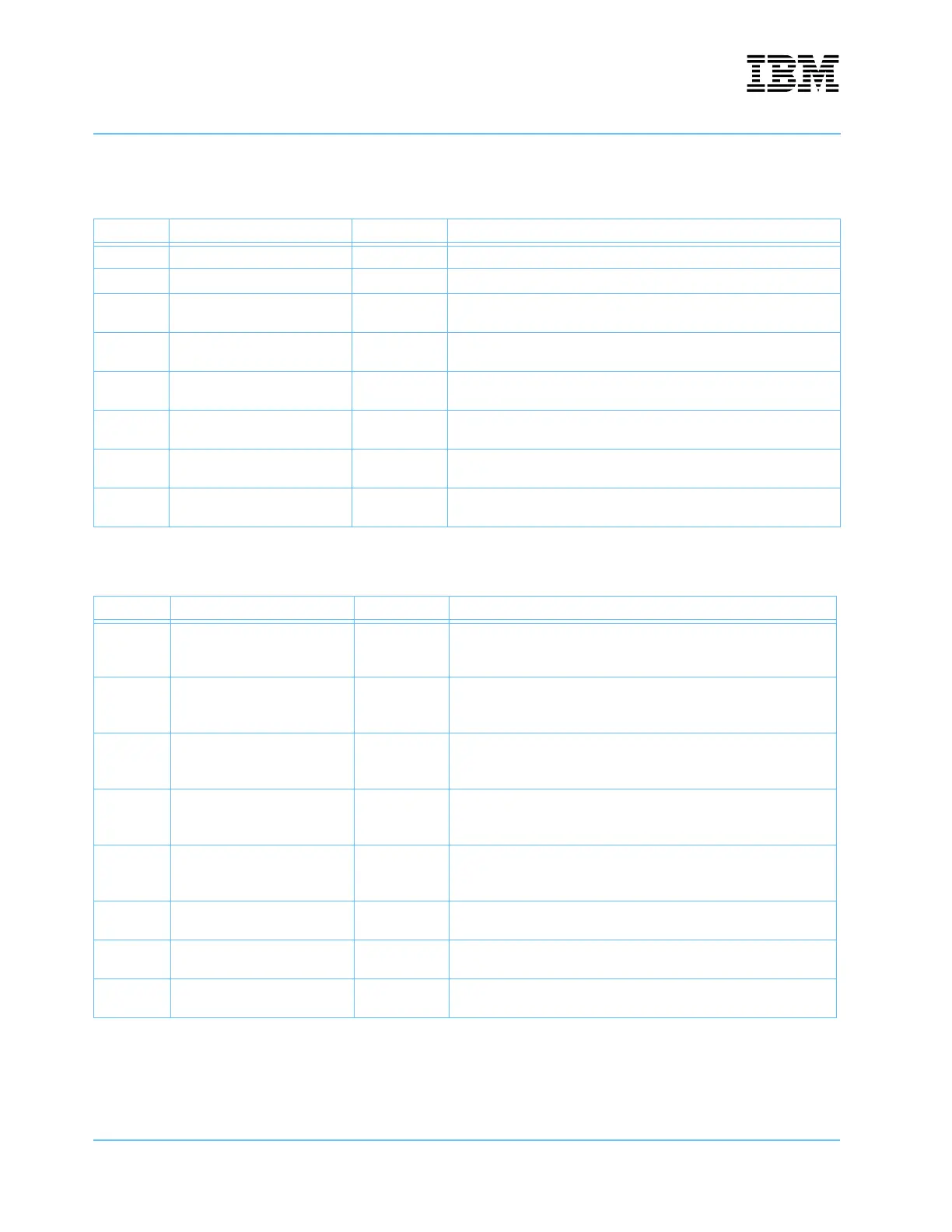

Table 3-4. Register2

Bit Name R/W Description

0 (msb) CPU1 MCP control R/W

Asserts the Machine Check Pin (MCP) signal on CPU1

0 = CPU1 MCP signal not asserted

1 = CPU1 MCP signal asserted

1 CPU0 MCP control R/W

Asserts the Machine Check Pin (MCP) signal on CPU0

0 = CPU0 MCP signal not asserted

1 = CPU0 MCP signal asserted

2 CPU TBEN control R/W

Controls the state of the timebase enable (TBEN) signal of both CPUs

0 = timebase runs freely on both CPUs

1 = timebase frozen on both CPUs

3 CPU1 SMI control R/W

Asserts the System Management Interrupt signal on CPU1

0 = CPU1 SMI signal not asserted

1 = CPU1 SMI signal asserted

4 CPU0 SMI control R/W

Asserts the System Management Interrupt signal on CPU0

0 = CPU0 SMI signal not asserted

1 = CPU0 SMI signal asserted

5 DS4 LED control R/W

0 = DS4 LED is ON

1 = DS4 LED is OFF

6 DS2 LED control R/W

0 = DS2 LED is ON

1 = DS2 LED is OFF

7 (lsb) DS1 LED control R/W

0 = DS1 LED is ON

1 = DS1 LED is OFF

Loading...

Loading...