Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

CPLD Programming

Page 76 of 115

750FXebm_ch11.fm

June 10, 2003

11.1.2 CPLD Logic

The folllowing sections provided a representation of the logic of the complete CPLD in either graphical or

code listing format.

GND+ 89

pld25mhz 90 Input

VCCINT 91 Power

dev_adr[0] 92 Bidir

dev_adr[1] 93 Bidir

dev_adr[2] 94 Bidir

GND 95 Gnd

dev_adr[3] 96 Bidir

dev_adr[4] 97 Bidir

ldev_addr[20] 98 Input

cpufan_ok_n 99 Input

ldev_addr[19] 100 Input

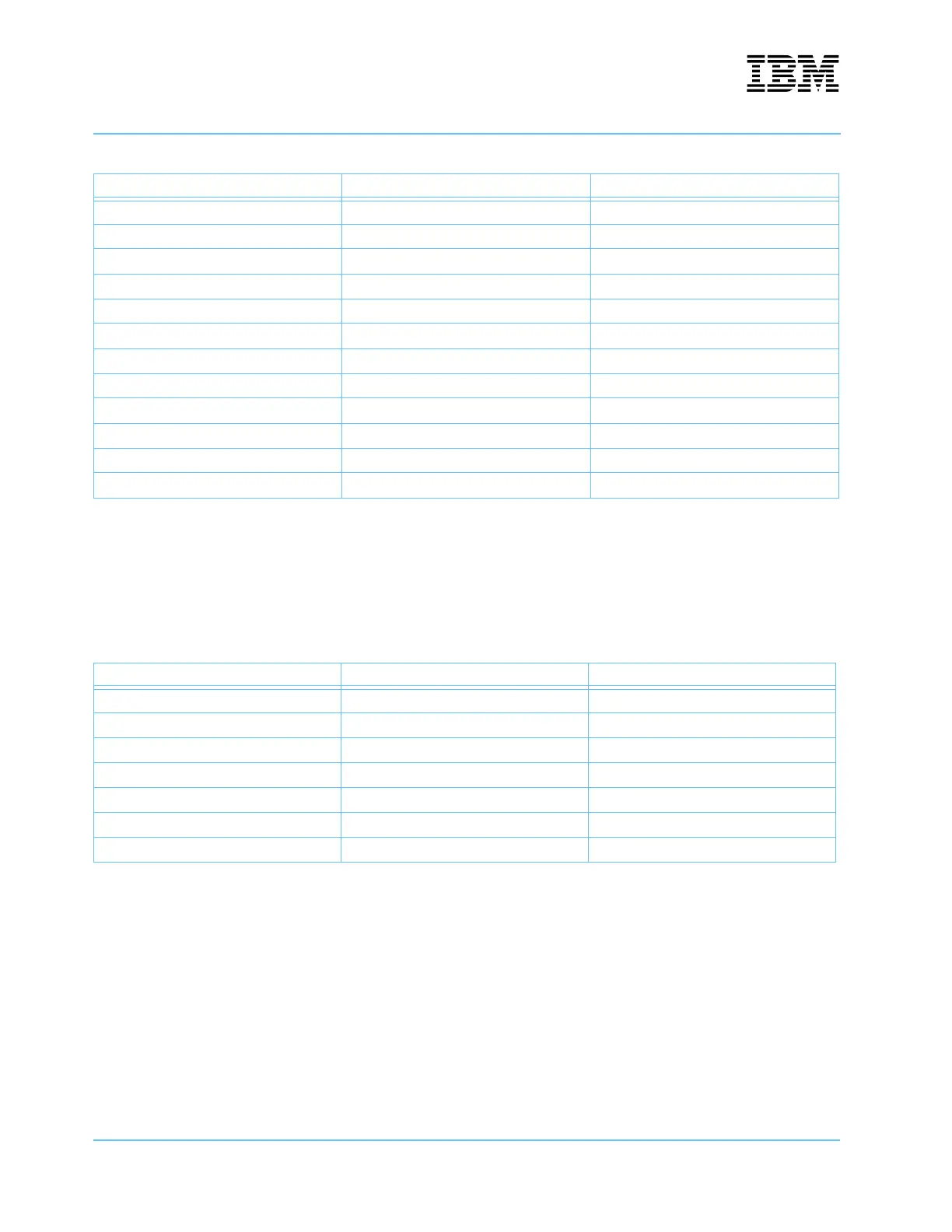

Table 11-3. CPLD Logic Descriptions

Section Description Page

Top Level Block Diagram 1 First three of five CPLD logic sections 77

Top Level Block Diagram 2 Last two of five CPLD logic sections 78

framcs Logic framcs detailed logic diagram 79

decode_block Program decode_block code listing 80

registers2 Program register2 code listing 84

reset_block Program reset_block code listing 89

misc Logic misc detailed logic diagram 93

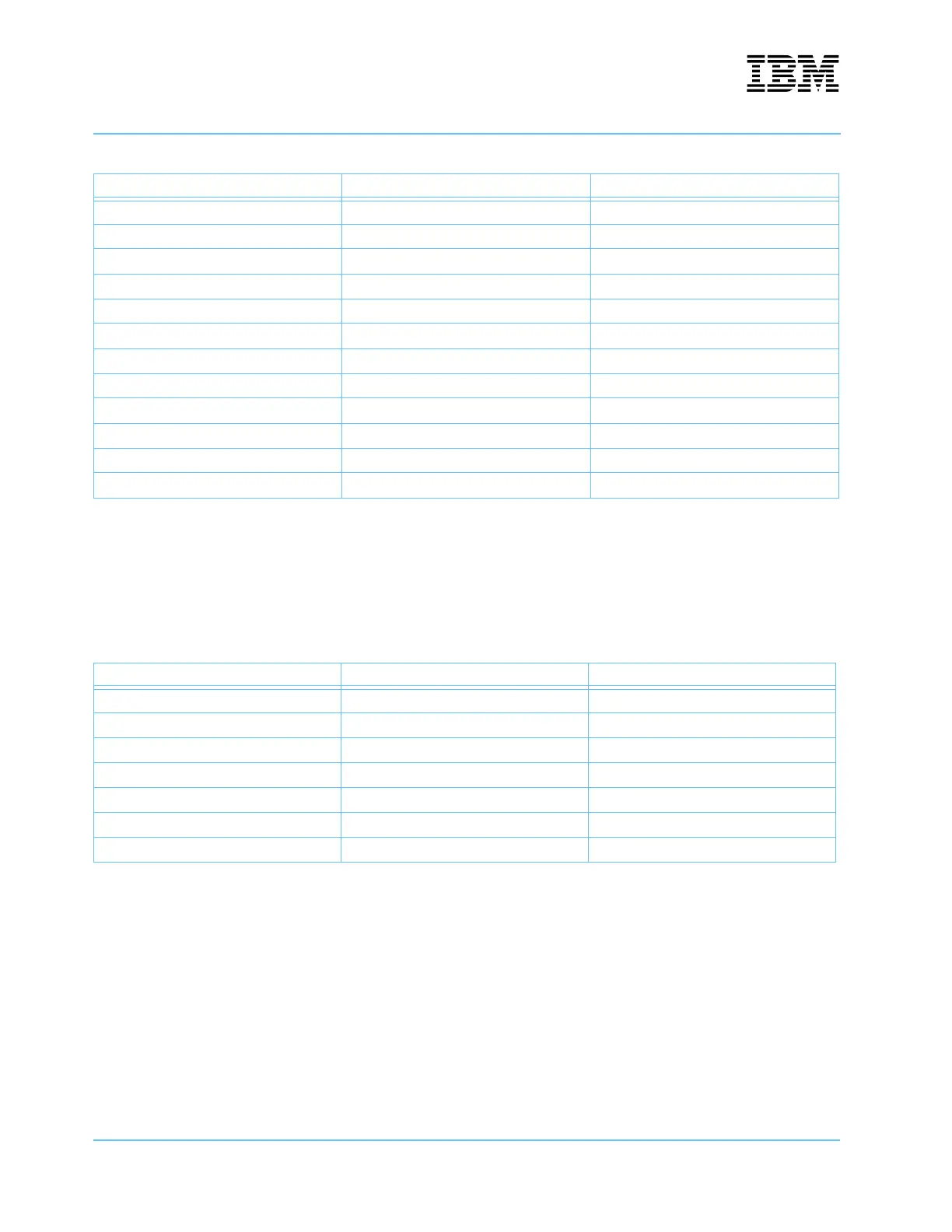

Table 11-2. CPLD I/O Pin List (Continued)

Name Pin Function

Loading...

Loading...