Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Programming the System Controller

Page 32 of 115

750FXebm_ch4.fm

June 10, 2003

4.2.1 Device Bank 0 Parameters (32-bit Flash)

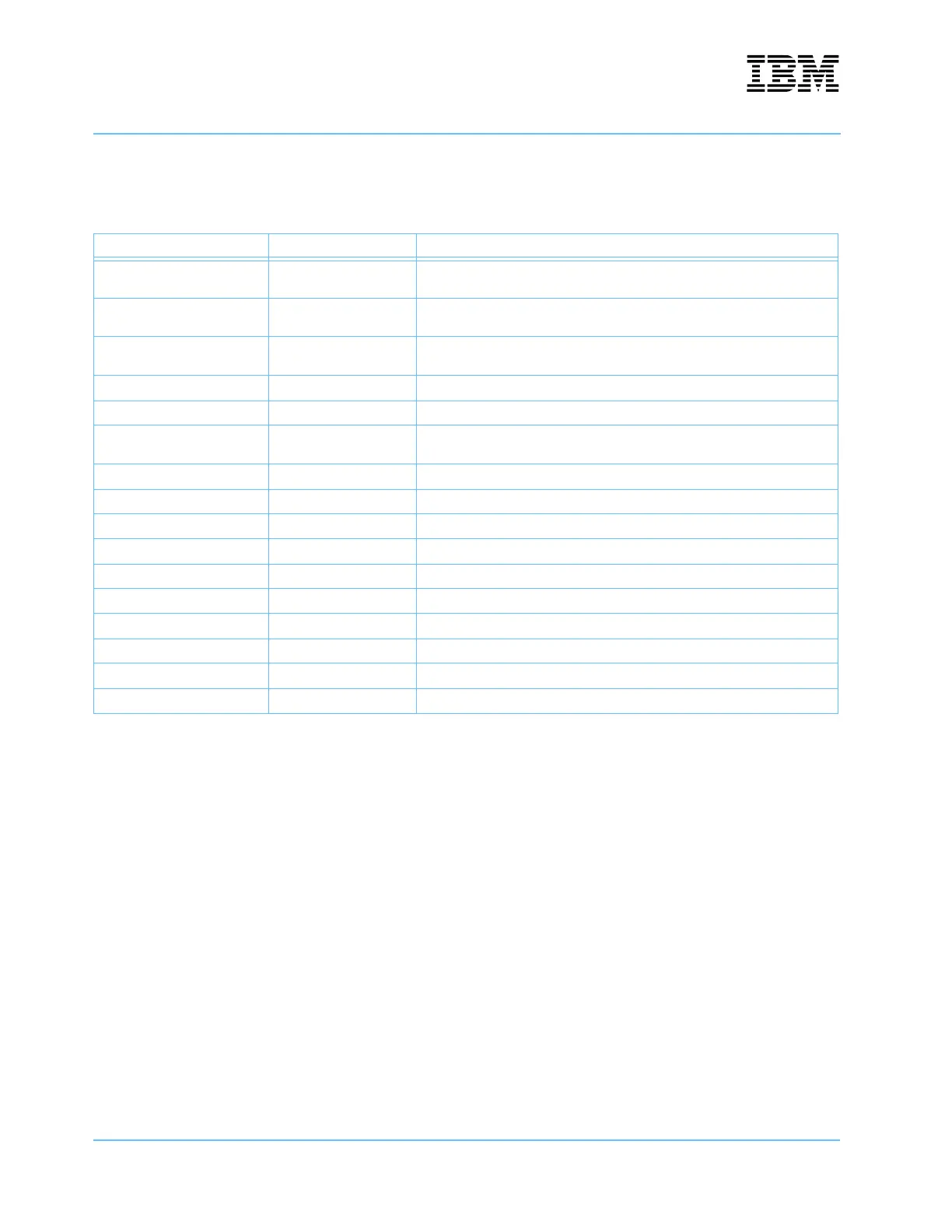

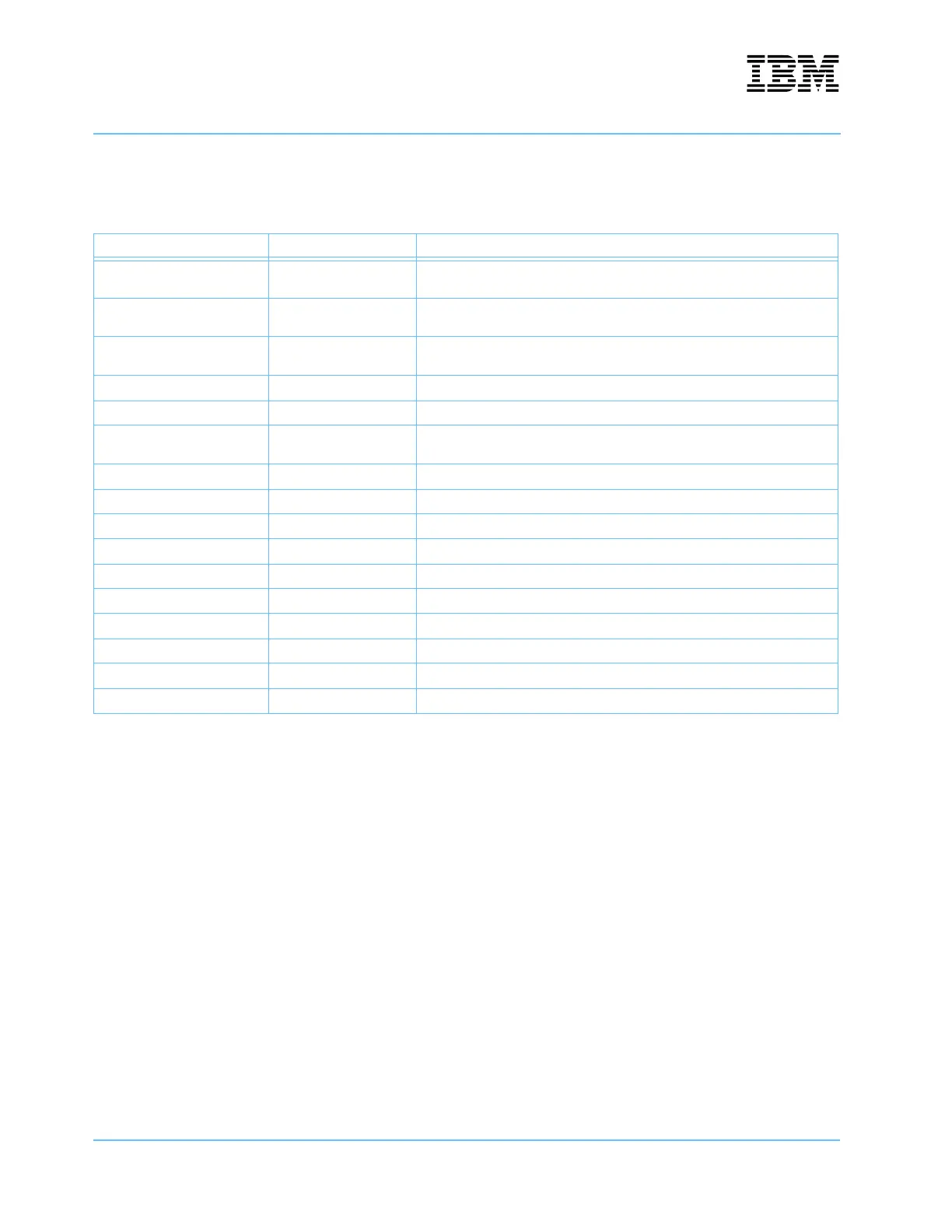

Table 4-2. Device Bank 0 Parameters = 0x85A492BF

Field Value (bin) Comment

TurnOff 111

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Acc2First 0111

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Acc2Next 0101

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

ALE2Wr 010 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 010 Number of Sysclk cycles that Wr[0] is active

WrHigh 010

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

DevWidth 10 Device width of 32 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 1 Acc2First extension (most significant bit)

Acc2NextExt 1 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 1 WrLow extension (most significant bit)

WrHighExt 0 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Loading...

Loading...