Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

CPLD Programming

Page 100 of 115

750FXebm_ch11.fm

June 10, 2003

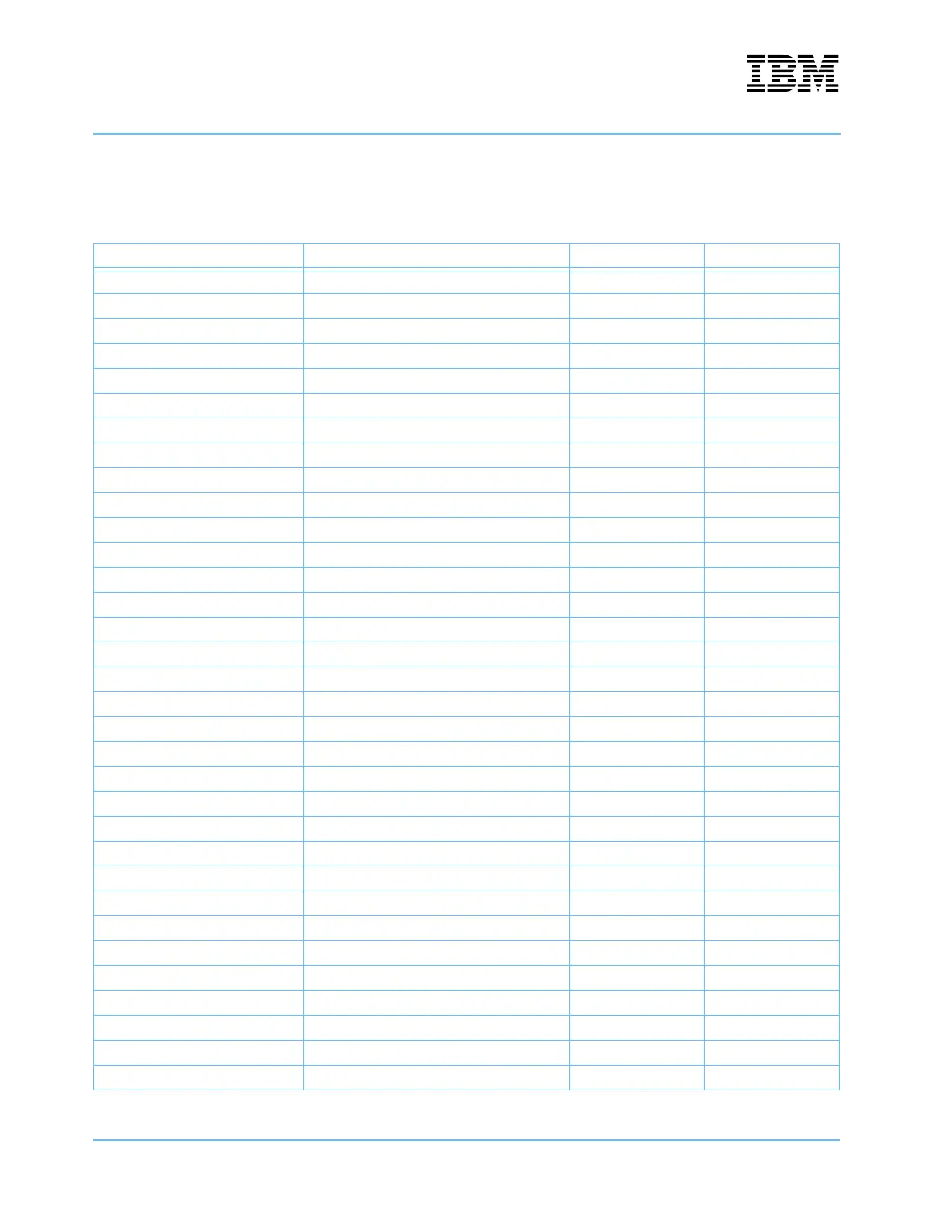

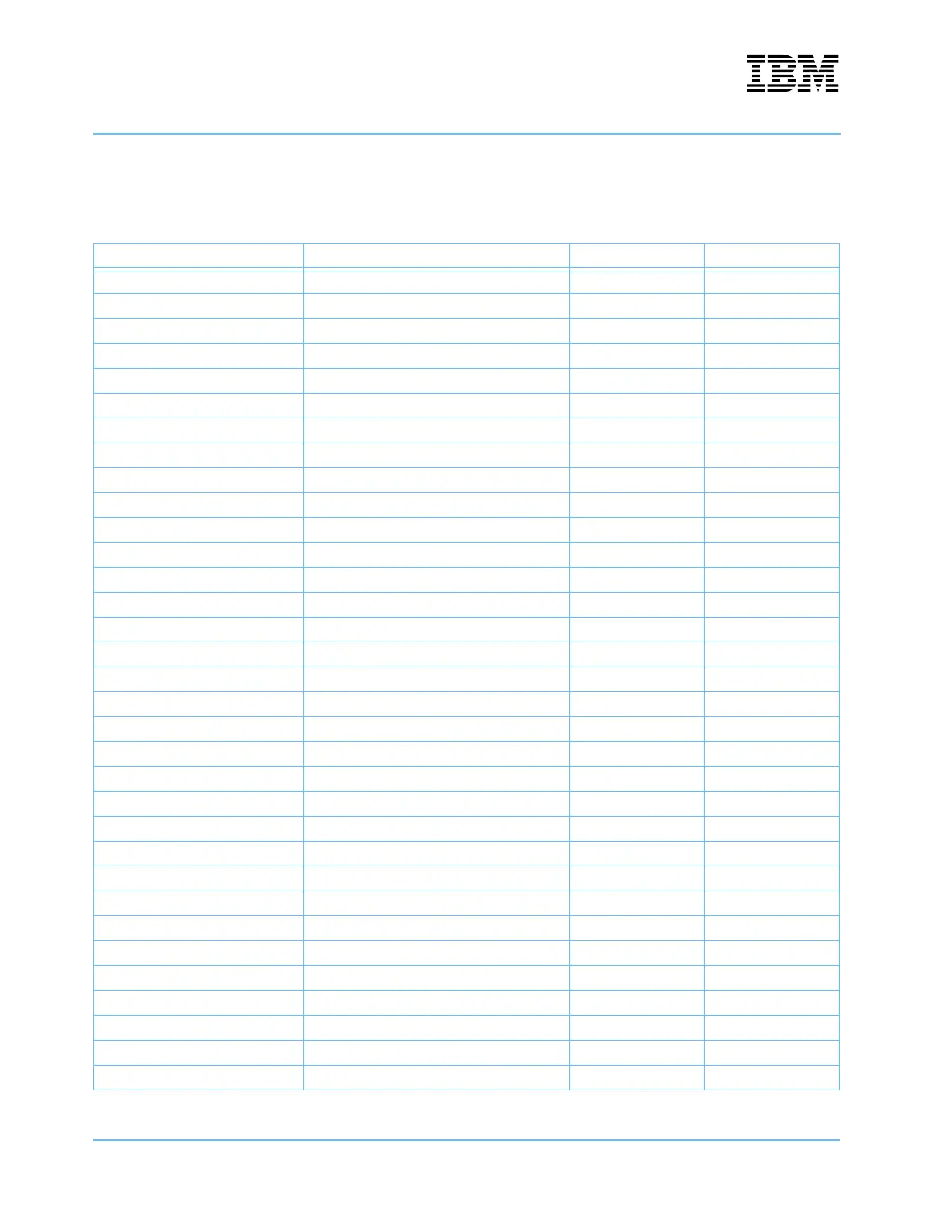

11.2.4 Setup and Hold Time

Table 11-7 provides the minimum setup and hold time for the indicated input relative to the indicated clock.

Table 11-7. Setup and Hold Time

Input Clock Setup Time (ns) Hold Time (ns)

atx_ok_n dev_we_n[0] 1.300 0.500

atx_ok_n pld25mhz 1.400 0.400

badr[0] dev_we_n[0] 3.100 0.200

badr[0] pld_sysclk 2.000 <= 0

badr[1] dev_we_n[0] 3.100 0.200

badr[1] pld_sysclk 2.000 <= 0

badr[2] dev_we_n[0] 3.100 0.200

badr[2] pld_sysclk 2.000 <= 0

bootsmall_n dev_we_n[0] 1.300 0.500

cstiming_n dev_we_n[0] 3.200 0.100

dev_adr[0] ale 1.400 0.400

dev_adr[0] dev_we_n[0] 1.000 0.800

dev_adr[0] pld25mhz -6.700 8.600

dev_adr[1] ale 1.500 0.300

dev_adr[1] dev_we_n[0] 1.100 0.700

dev_adr[2] dev_we_n[0] 1.000 0.800

dev_adr[3] dev_we_n[0] 1.000 0.800

dev_adr[4] dev_we_n[0] 1.000 0.800

dev_adr[5] dev_we_n[0] 1.000 0.800

dev_adr[6] dev_we_n[0] 1.000 0.800

dev_adr[7] dev_we_n[0] 1.000 0.800

flash_n/sram_sel dev_we_n[0] 1.300 0.500

lcs_n[1] dev_we_n[0] 2.900 0.400

lcs_n[3] pld_sysclk 1.500 0.300

pci_reset_n pld25mhz 1.700 0.100

pwrgd pld25mhz 5.200 <= 0

rw_hreset pld25mhz 1.500 0.300

rw_sreset pld25mhz 1.500 0.300

rw_trst pld25mhz 1.500 0.300

switch_a dev_we_n[0] 1.400 0.400

switch_b dev_we_n[0] 1.400 0.400

target/host_n dev_we_n[0] 1.300 0.500

target/host_n pld25mhz 1.400 0.400

Loading...

Loading...