Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

CPLD Programming

Page 96 of 115

750FXebm_ch11.fm

June 10, 2003

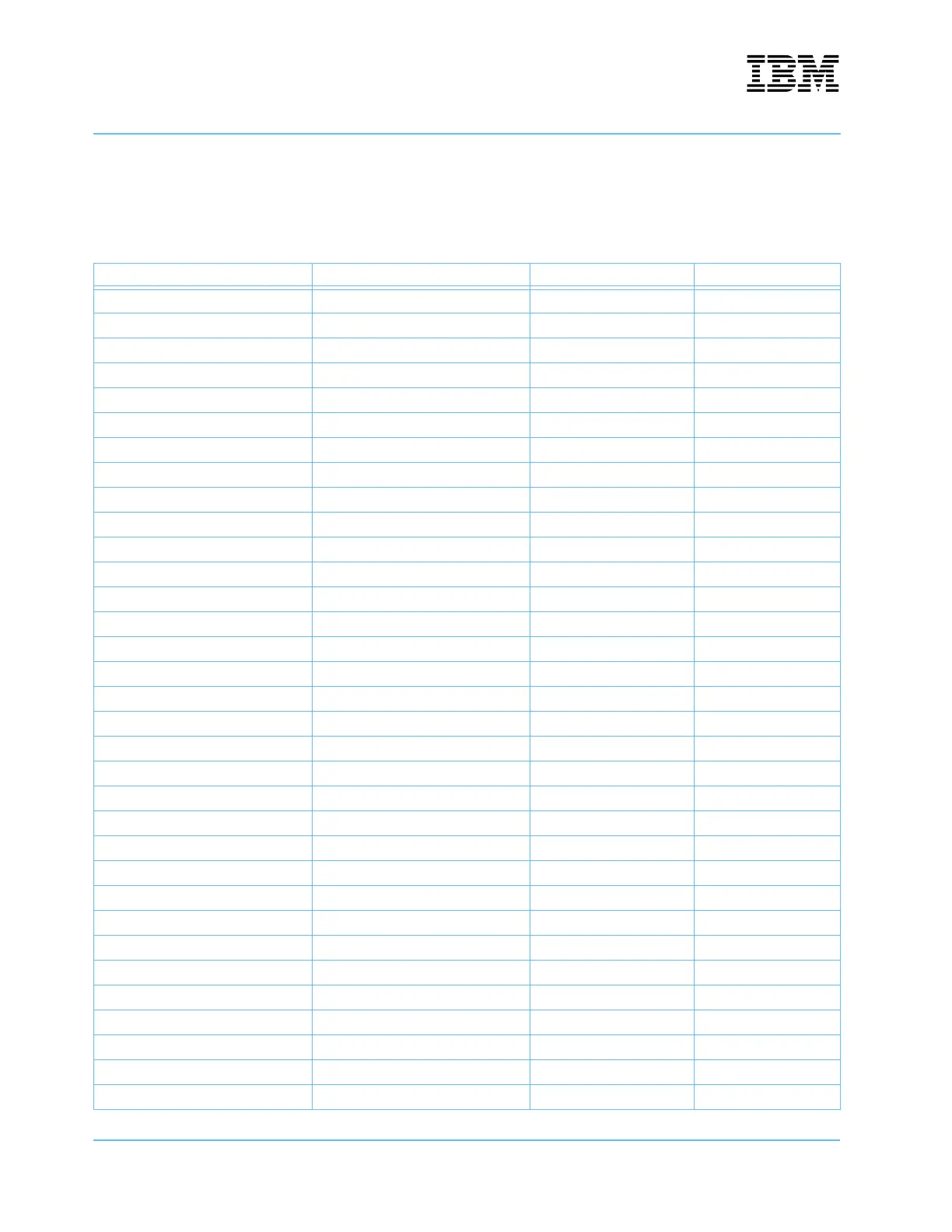

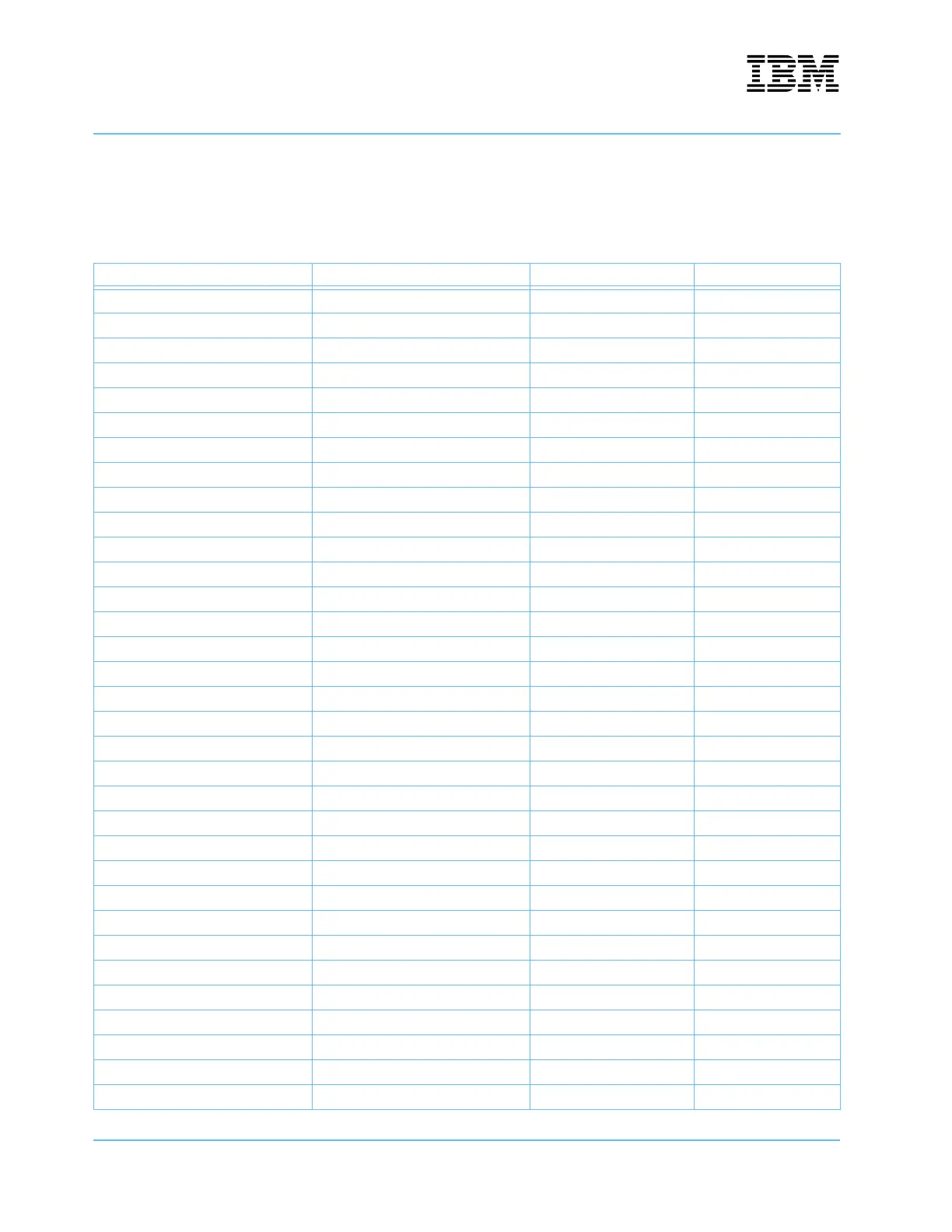

11.2.3 Pin-to-Pin Signal Delay

Table 11-6 provides the input pin-to-output pin delay time for all signals that are not clocked through a

register.

Table 11-6. Pin-to-Pin Signal Delay

Source Destination Longest Delay (ns) Shortest Delay (ns)

atx_ok_n cpu_trst_n 14.200 14.200

atx_ok_n cpu0_hreset_n 10.900 10.500

atx_ok_n cpu1_hreset_n 14.200 14.200

atx_ok_n led_red_n 5.300 5.300

atx_ok_n sysreset 10.300 10.300

atx_ok_n sysreset_n 10.300 10.300

badr[0] dev_adr[0] 8.700 5.600

badr[0] dev_adr[1] 8.700 5.600

badr[0] dev_adr[2] 8.700 5.600

badr[0] dev_adr[3] 8.700 5.600

badr[0] dev_adr[4] 8.700 5.600

badr[0] dev_adr[5] 8.700 5.600

badr[0] dev_adr[6] 8.700 5.600

badr[0] dev_adr[7] 8.700 5.600

badr[0] nvram_cs_n 14.300 14.300

badr[0] uart_cs_n 5.600 5.600

badr[0] write_n 6.400 5.600

badr[1] dev_adr[0] 8.700 5.600

badr[1] dev_adr[1] 8.700 5.600

badr[1] dev_adr[2] 8.700 5.600

badr[1] dev_adr[3] 8.700 5.600

badr[1] dev_adr[4] 8.700 5.600

badr[1] dev_adr[5] 8.700 5.600

badr[1] dev_adr[6] 8.700 5.600

badr[1] dev_adr[7] 8.700 5.600

badr[1] nvram_cs_n 14.300 14.300

badr[1] uart_cs_n 5.600 5.600

badr[1] write_n 6.400 5.600

badr[2] dev_adr[0] 8.700 5.600

badr[2] dev_adr[1] 8.700 5.600

badr[2] dev_adr[2] 8.700 5.600

badr[2] dev_adr[3] 8.700 5.600

badr[2] dev_adr[4] 8.700 5.600

Loading...

Loading...