Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

750FXebm_ch11.fm

June 10, 2003

CPLD Programming

Page 99 of 115

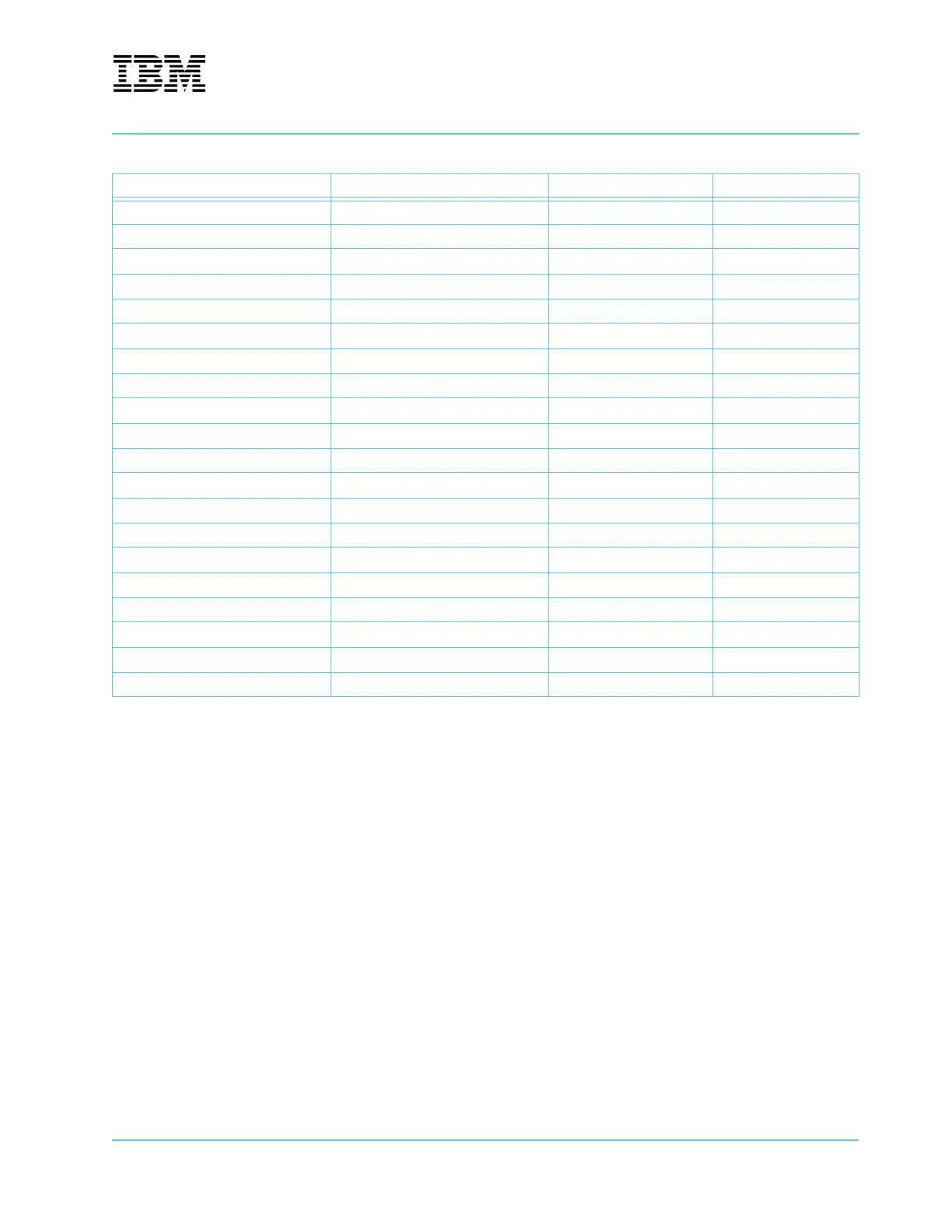

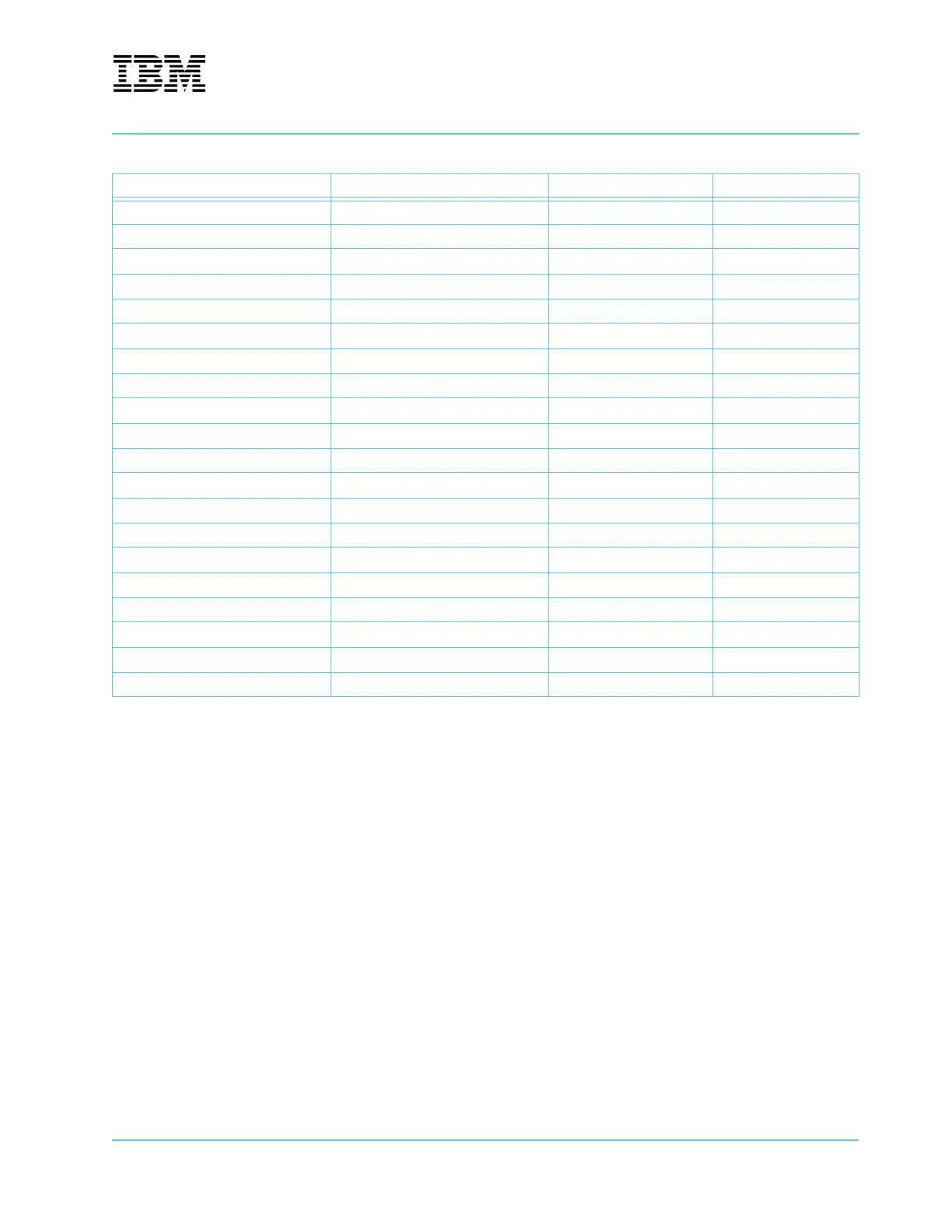

ldev_addr[20] sram_cs_n 5.200 5.200

ldev_addr[20] sram_hi_cs_n 5.200 5.200

ldev_addr[20] textpin_d 5.400 5.400

mpp0_hreset_n cpu0_hreset_n 10.600 10.200

mpp0_sreset_n cpu0_sreset_n 10.200 10.200

mpp1_hreset_n cpu1_hreset_n 14.700 13.900

mpp1_sreset_n cpu1_sreset_n 10.200 10.200

pci_reset_n cpu_trst_n 14.500 14.100

pci_reset_n cpu0_hreset_n 11.200 10.400

pci_reset_n cpu1_hreset_n 14.900 14.500

pci_reset_n led_red_n 5.200 5.200

pci_reset_n sysreset 10.200 10.200

pci_reset_n sysreset_n 10.200 10.200

target/host_n cpu_trst_n 14.200 14.200

target/host_n cpu0_hreset_n 10.900 10.500

target/host_n cpu1_hreset_n 14.600 14.200

target/host_n led_red_n 5.300 5.300

target/host_n pci_reset_n 4.300 4.300

target/host_n sysreset 10.300 10.300

target/host_n sysreset_n 10.300 10.300

Table 11-6. Pin-to-Pin Signal Delay (Continued)

Source Destination Longest Delay (ns) Shortest Delay (ns)

Loading...

Loading...