Development Kit Features

2

nd

Generation Intel

®

Core™ Processor with Intel

®

6 Series Chipset Development Kit

March 2011 User Guide

Document Number: 325208-001 39

IO headers are provided for the other eight USB lanes. Port 4 is also routed to

docking. To enable USB port 4 to docking, STUFF R8U3, R8U5 and UNSTUFF R8F4,

R8F6.

Overcurrent protection has been provided for ports in pairs. Ports (0,1), (1,2)…

(12,13) share the OC Indicators.

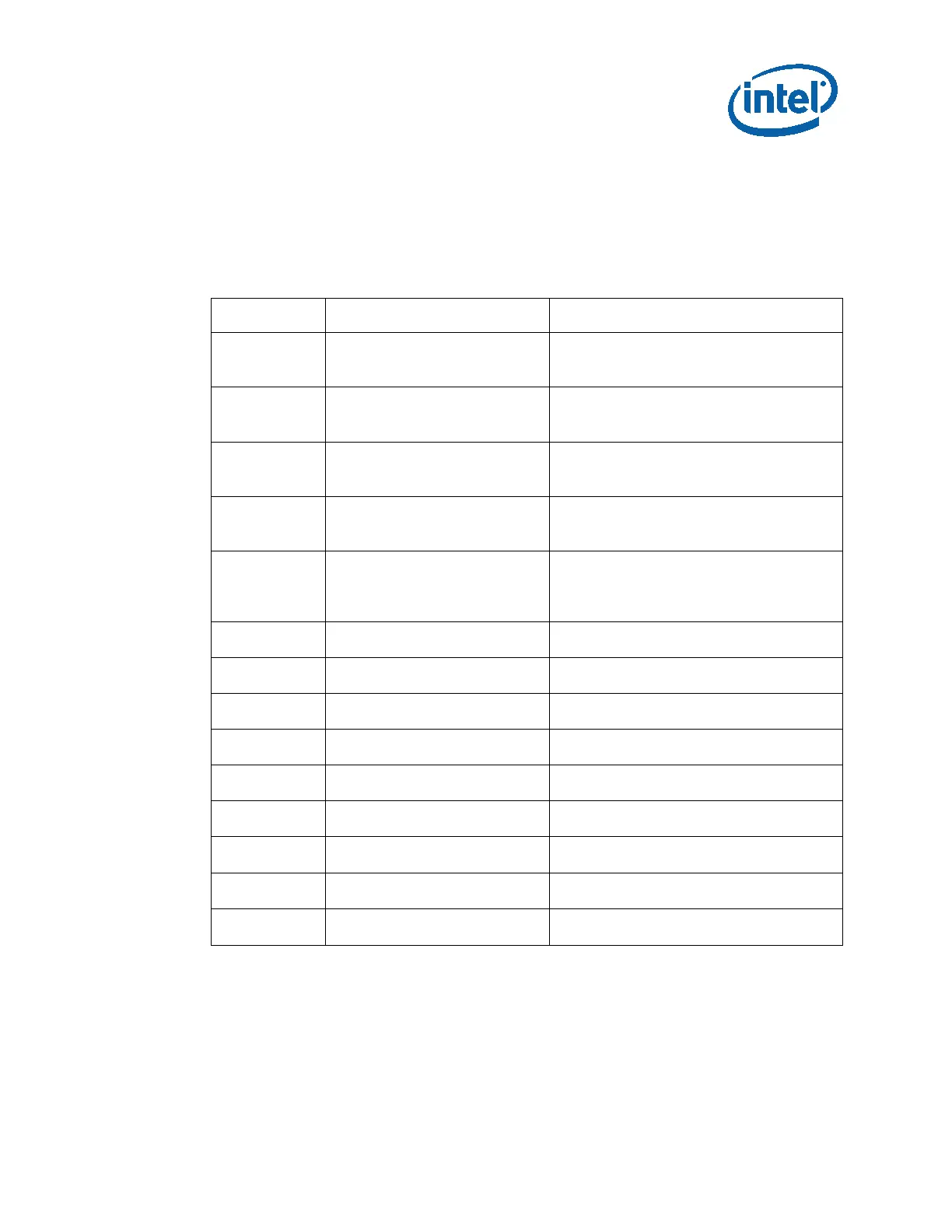

Table 12. USB Port Mapping

USB Port Panel Connector

Port 0 Back Panel I/O Connector J5A1 (stacked dual USB and DP connector)

Port 1 Back Panel I/O Connector J5A1 (stacked dual USB and DP connector)

Port 2 Back Panel I/O Connector J3A2 (stacked dual USB2.0 connector)

Port 3 Back Panel I/O Connector J3A2 (stacked dual USB2.0 connector)

Port 4 FPIO

Docking connector(J9C1) Option to J8H2

(2x5 Connector)

Port 5 FPIO J8H2 (2x5 Connector)

Port 6 FPIO J7H5 (2x5 Connector)

Port 7 FPIO J7H5 (2x5 Connector)

Port 8 Back Panel J4A1

Port 9 Back Panel J4A1

Port 10 FPIO J7H6 (2x5 Connector)

Port 11 FPIO J7H6 (2x5 Connector)

Port 12 FPIO J7H2 (2x5 Connector)

Port 13 FPIO J7H2 (2x5 Connector)

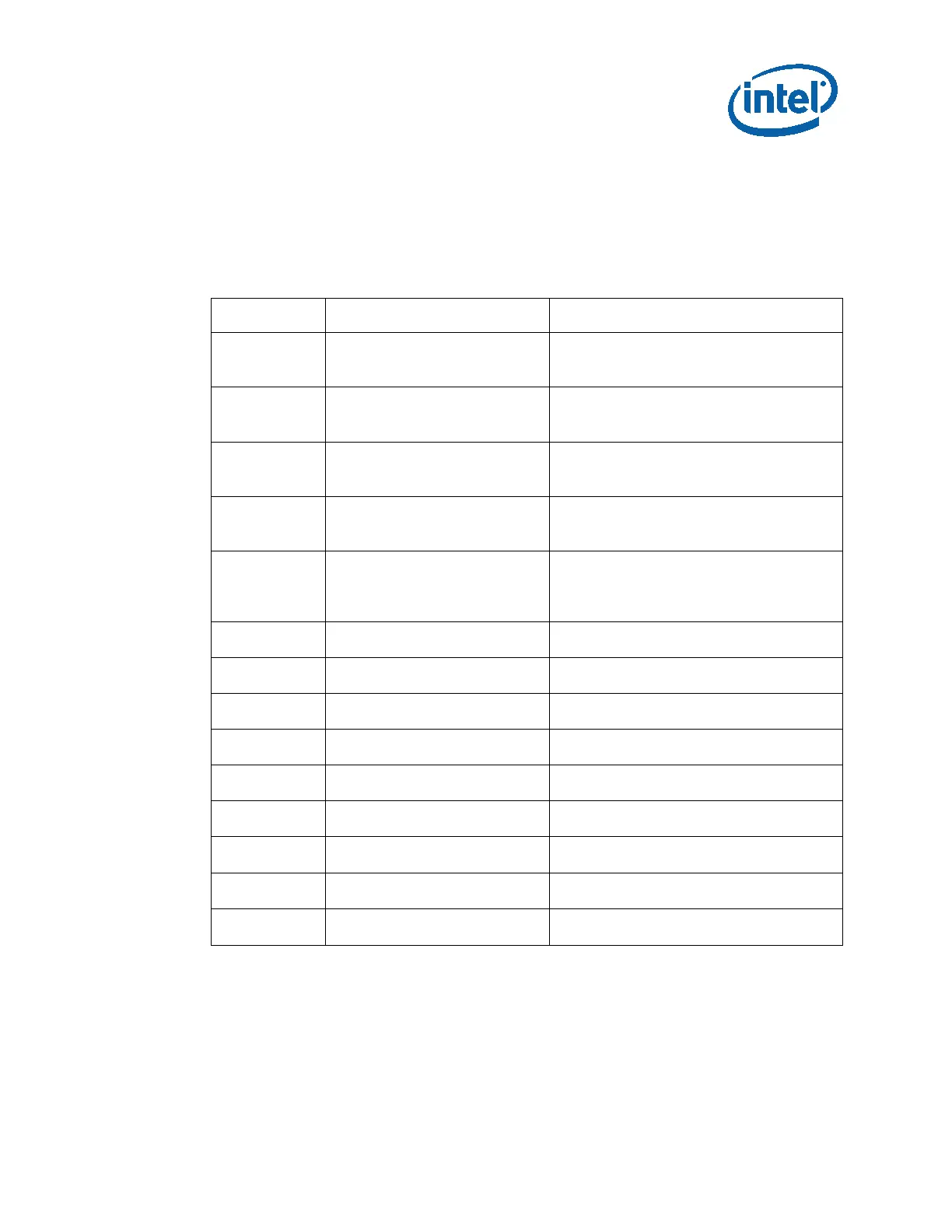

The table below indicates the OC mapping for all the USB2.0 ports.

Loading...

Loading...