24

www.lannerinc.com

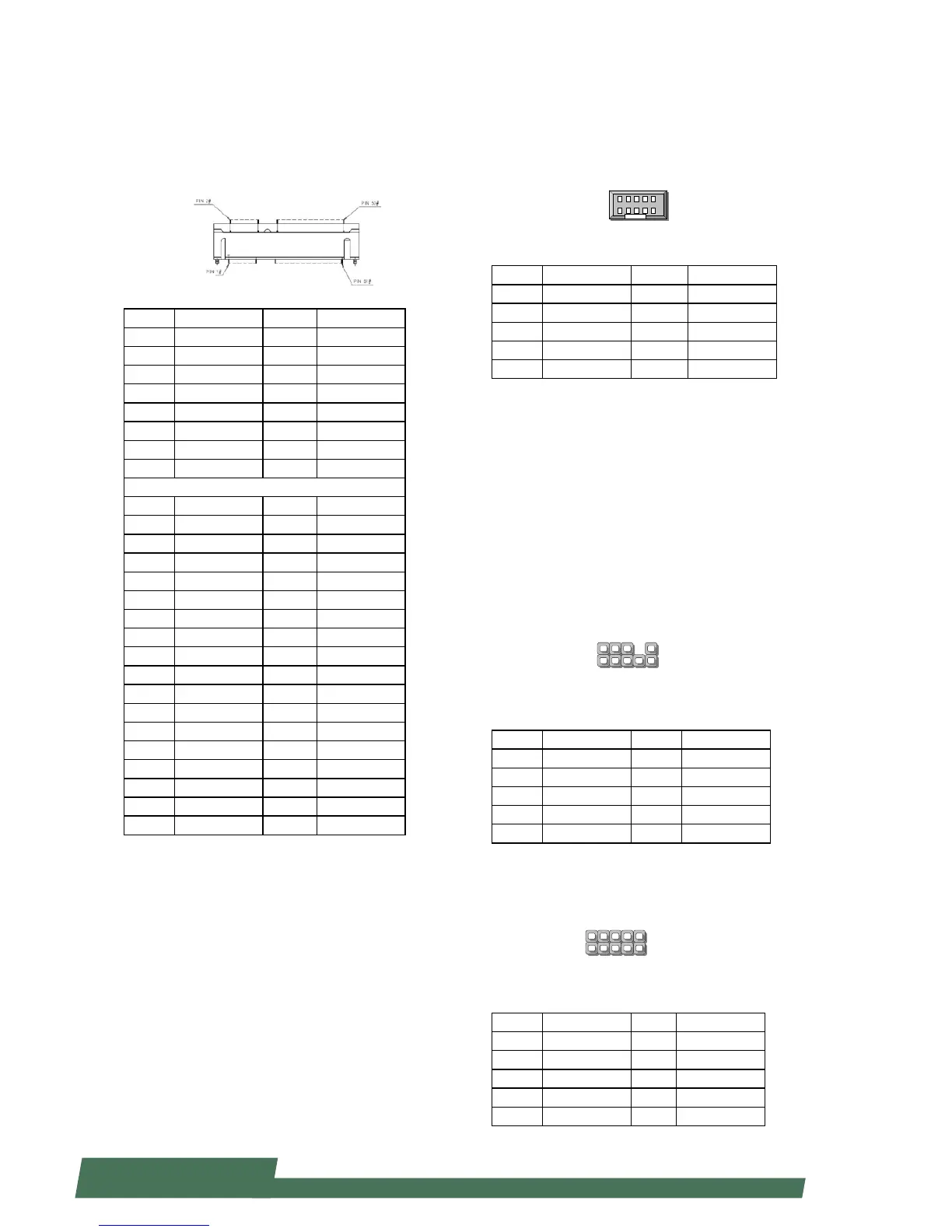

Mini-PCIe socket (MPCIE1):

Serves as mSATA storage socket

Pin Description Pin Description

1 NC 2 3.3V

3 NC 4 GND

5 NC 6 NC

7 NC 8 NC

9 GND 10 NC

11 PCIe Clock_N 12 NC

13 PCIe Clock_P 14 NC

15 GND 16 NC

Mechanical key

17 NC 18 3.3V

19 NC 20 NC

21 GND 22 PCIe Reset#

23 SATA_RX_N 24 3.3V

25 SATA_RX_P 26 GND

27 GND 28 NC

29 GND 30 NC

31 SATA_TX_N 32 NC

33 SATA_TX_P 34 GND

35 GND 36 NC

37 GND 38 NC

39 3.3V 40 GND

41 3.3V 42 NC

43 GND 44 NC

45 NC 46 NC

47 NC 48 NC

49 Active#/LED 50 GND

51 NC 52 3.3V

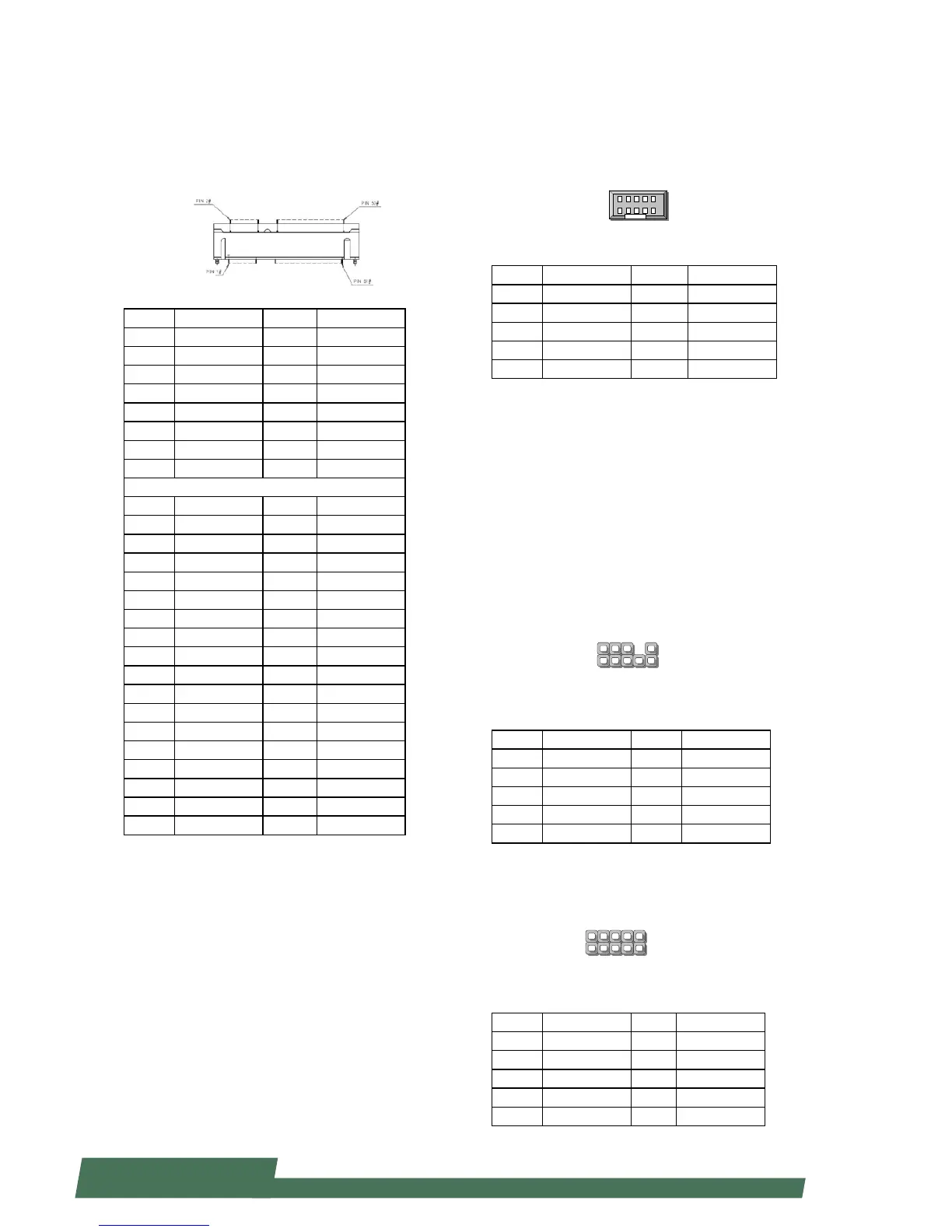

USB connector (USBA1)

Pin Description Pin Description

1 5V 2 5V

3 USB2- 4 USB3-

5 USB2+ 6 USB3+

7 USB23GND 8 USB23GND

9 USB23GND 10 USB23GND

Security Override (JSDO23)

FLASH DESCRIPTOR SECURITY OVERRIDE WHEN HIGH

(Default Not Connect)

Port 80 (J13): This is the Port 80h, which is used as

BIOS debug port. Once the system is initialized, BIOS

will send POST (Power-On Self-Test) codes to Port 80.

If POST fails, the last generated POST code will be left

in Port 80. This is used for debug purpose. If a seven-

segment display is connected, the hexadecimal BIOS

debug code will appear.

Pin Description Pin Description

1 CLK_33M_P80 2 LPC_LAD_1

3 RST_PORT80_N 4 LPC_LAD_0

5 LPC_FRAME_N 6 3.3V

7 LPC_LAD_3 8 X

9 LPC_LAD_2 10 GND

SPIROM1:

SPI ROM pin header

Pin Description Pin Description

1 No Connect 2 No Connect

3 Dual_CS00_N 4 3.3V

5 SPI_MISO_DUAL 6 SPI_HOLD0_L

7 No Connect 8 SPI_CLK_DUAL

9 GND 10 SPI_MOSI_DUAL

Loading...

Loading...