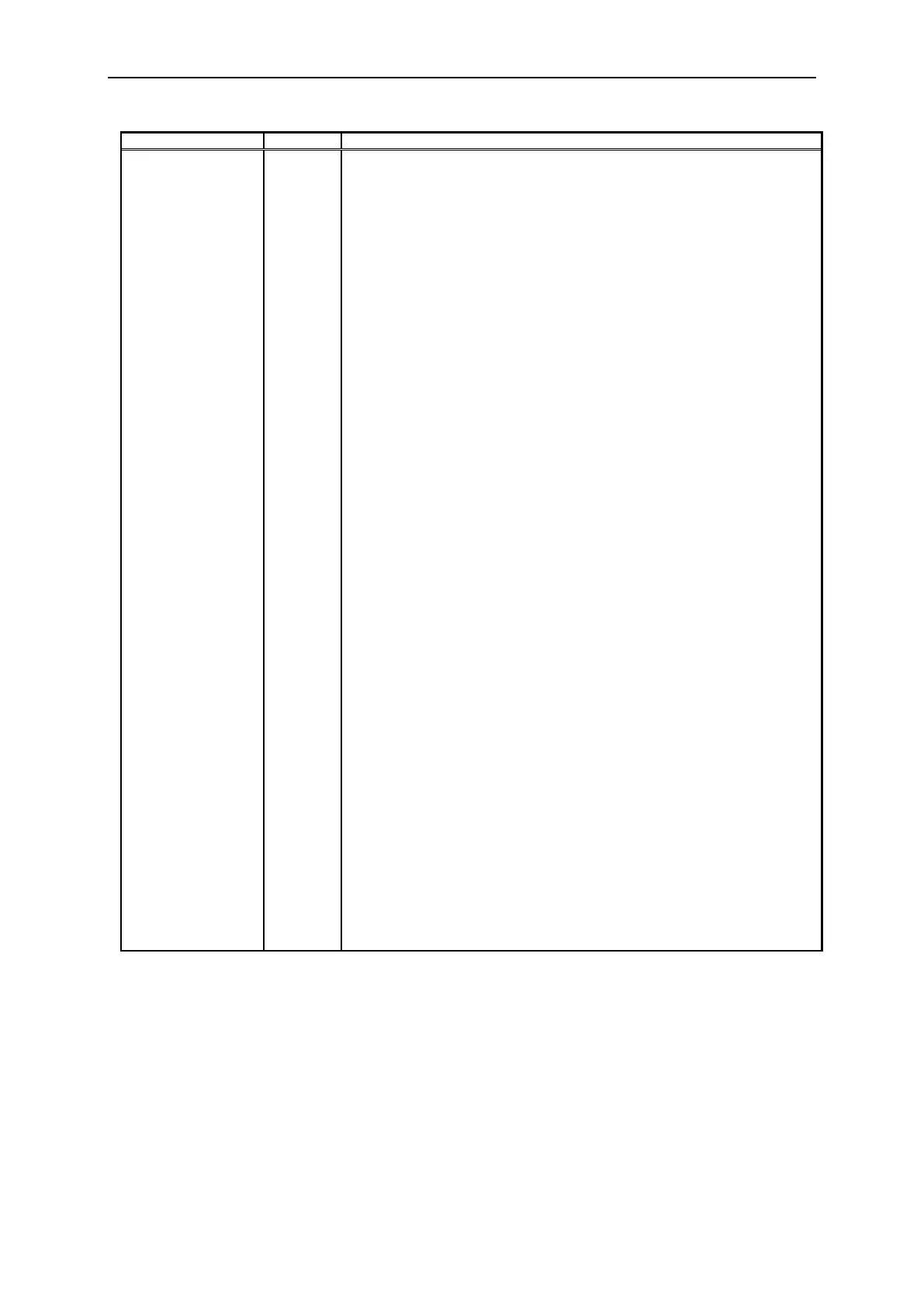

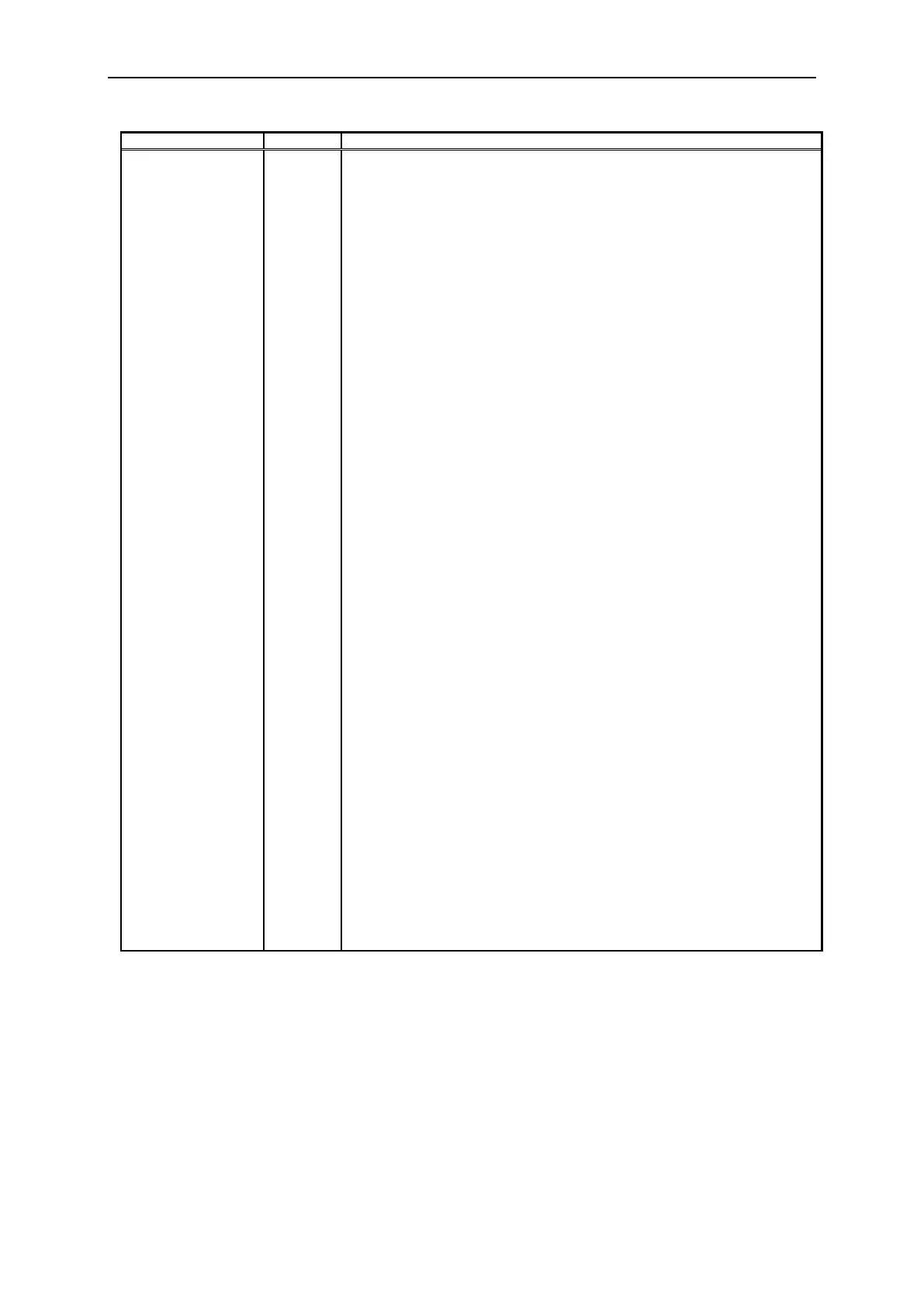

LRST_TX_B: Resets all the logic registers to the default state for Tx MIMO channel

B.

0 – Reset active

1 – Reset inactive (default)

MRST_TX_B: Resets all the configuration memory to the default state for Tx MIMO

channel B.

0 – Reset active

1 – Reset inactive (default)

LRST_TX_A: Resets all the logic registers to the default state for Tx MIMO channel

A.

0 – Reset active

1 – Reset inactive (default)

MRST_TX_A: Resets all the configuration memory to the default state for Tx MIMO

channel A.

0 – Reset active

1 – Reset inactive (default)

LRST_RX_B: Resets all the logic registers to the default state for Rx MIMO channel

B.

0 – Reset active

1 – Reset inactive (default)

MRST_RX_B: Resets all the configuration memory to the default state for Rx MIMO

channel B.

0 – Reset active

1 – Reset inactive (default)

LRST_RX_A: Resets all the logic registers to the default state for Rx MIMO channel

A.

0 – Reset active

1 – Reset inactive (default)

MRST_RX_A: Resets all the configuration memory to the default state for Rx MIMO

channel A.

0 – Reset active

1 – Reset inactive (default)

SRST_RXFIFO: RX FIFO soft reset (LimeLight

TM

Interface).

0 – Reset active

1 – Reset inactive (default)

SRST_TXFIFO: TX FIFO soft reset (LimeLight

TM

Interface).

0 – Reset active

1 – Reset inactive (default)

RXEN_B: Power control for Rx MIMO channel B.

0 – Rx MIMO channel B powered down

1 – Rx MIMO channel B enabled (default)

RXEN_A: Power control for Rx MIMO channel A.

0 – Rx MIMO channel A powered down

1 – Rx MIMO channel A enabled (default)

TXEN_B: Power control for Tx MIMO channel B.

0 – Tx MIMO channel B powered down

1 – Tx MIMO channel B enabled (default)

TXEN_A: Power control for Tx MIMO channel A.

0 – Tx MIMO channel A powered down

1 – Tx MIMO channel A enabled (default)

MAC[1:0]: MIMO access control.

11 – Channels A and B accessible. SPI write operation only (default)

01 – Channel A accessible only. Valid for SPI read/write

10 – Channel B accessible only. Valid for SPI read/write

Default: 11111111 11111111

Loading...

Loading...