69

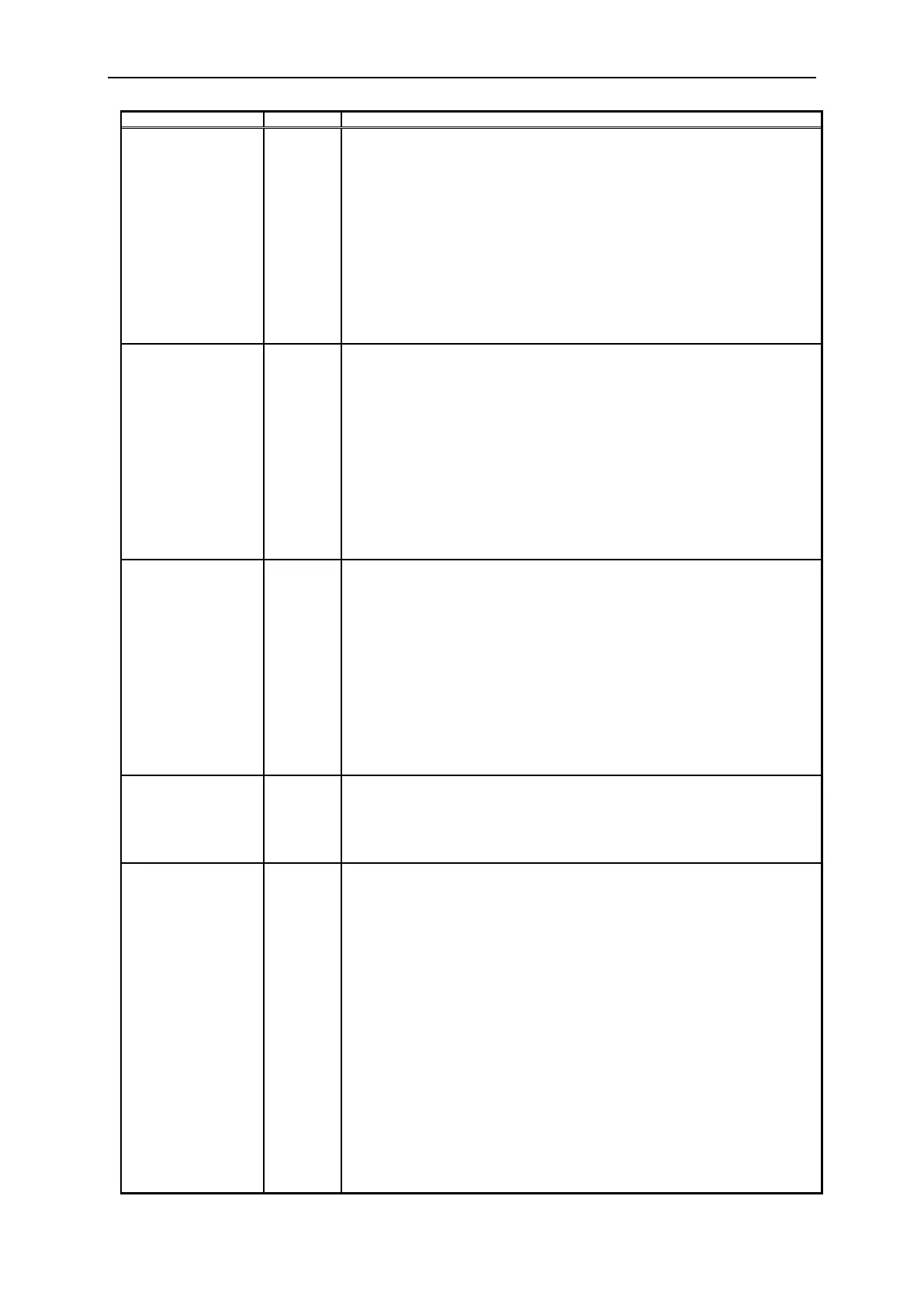

DCWR_RXAQ. Used to enable manual write operation of RXAQ DAC values. Value

must be first stored in DC_RXAQ register prior to toggling this flag:

0 to 1 –writes the value to RXAQ DAC from DC_RXAQ register Default: 0

DCRD_RXAQ. Used to enable manual read operation of RXAQ DAC values:

0 to 1 – read the value from RXAQ DAC to DC_RXAQ register Default: 0

Reserved

DC_RXAQ[6:0]: Stores the value to be written to the as well as read value from

RXAQ DAC. Default: 0

DC_RXAQ[6] – sign

DC_RXAQ[5:0] – magnitude

Default: 00000000 00000000

DCWR_RXBI. Used to enable manual write operation of RXBI DAC values. Value

must be first stored in DC_RXBI register prior to toggling this flag:

0 to 1 – writes the value to RXBI DAC from DC_RXBI register Default: 0

DCRD_RXBI. Used to enable manual read operation of RXBI DAC values:

0 to 1 – read the value from RXBI DAC to DC_RXBI register Default: 0

Reserved

DC_RXBI[6:0]: Stores the value to be written to the as well as read value from RXBI

DAC. Default: 0

DC_RXBI[6] – sign

DC_RXBI[5:0] – magnitude

Default: 00000000 00000000

DCWR_RXBQ. Used to enable manual write operation of RXBQ DAC values. Value

must be first stored in DC_RXBQ register prior to toggling this flag:

0 to 1 –writes the value to RXBQ DAC from DC_RXBQ register Default: 0

DCRD_RXBQ. Used to enable manual read operation of RXBQ DAC values:

0 to 1 – read the value from RXBQ DAC to DC_RXBQ register Default: 0

Reserved

DC_RXBQ[6:0]: Stores the value to be written to the as well as read value from

RXBQ DAC. Default: 0

DC_RXBQ[6] – sign

DC_RXBQ[5:0] – magnitude

Default: 00000000 00000000

DC_RXCDIV[7:0]: Clock division ratio for Rx DC calibration loop

0 to 255 – Division ratio is n+1 Default: 31

DC_TXCDIV[7:0]: Clock division ratio for Tx DC calibration loop

0 to 255 – Division ratio is n+1 Default: 15

Default: 00011111 00001111

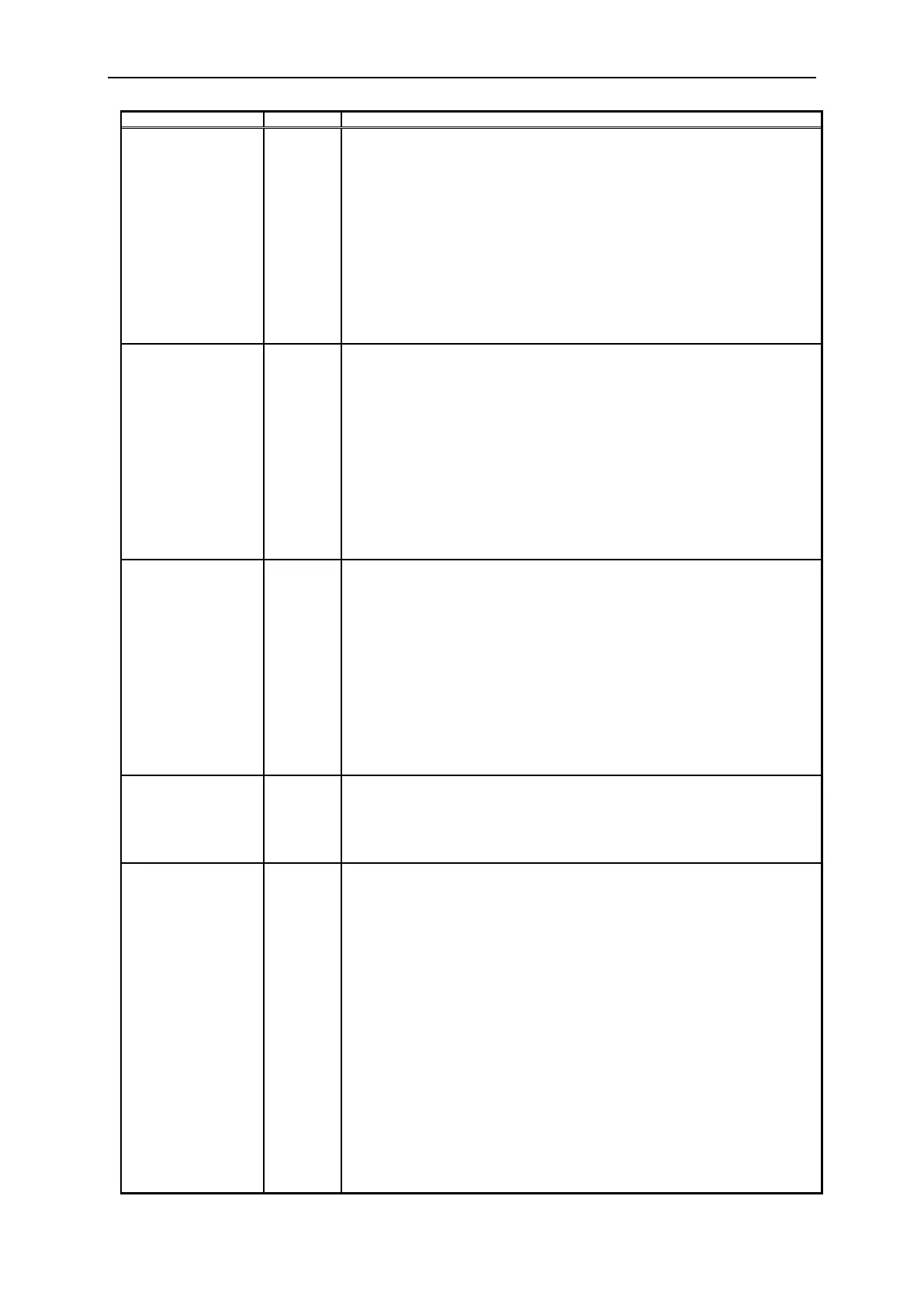

15 – 12

11 – 9

8 – 6

5 – 3

2 – 0

Reserved

DC_HYSCMP_RXB[2:0]: Comparator hysteresis control, RXB channel

0 – min hysteresis (default)

...

7 – max hysteresis

DC_HYSCMP_RXA[2:0]: Comparator hysteresis control, RXA channel

0 – min hysteresis (default)

...

7 – max hysteresis

DC_HYSCMP_TXB[2:0]: Comparator hysteresis control, TXB channel

0 – min hysteresis (default)

...

7 – max hysteresis

DC_HYSCMP_TXA[2:0]: Comparator hysteresis control, TXA channel

0 – min hysteresis (default)

...

7 – max hysteresis

Default: 00000000 00000000

Loading...

Loading...