4

bit register address when concatenated ((Maddress << 6) | Reg). Use global address values for

particular register from the tables provided in Section 2.

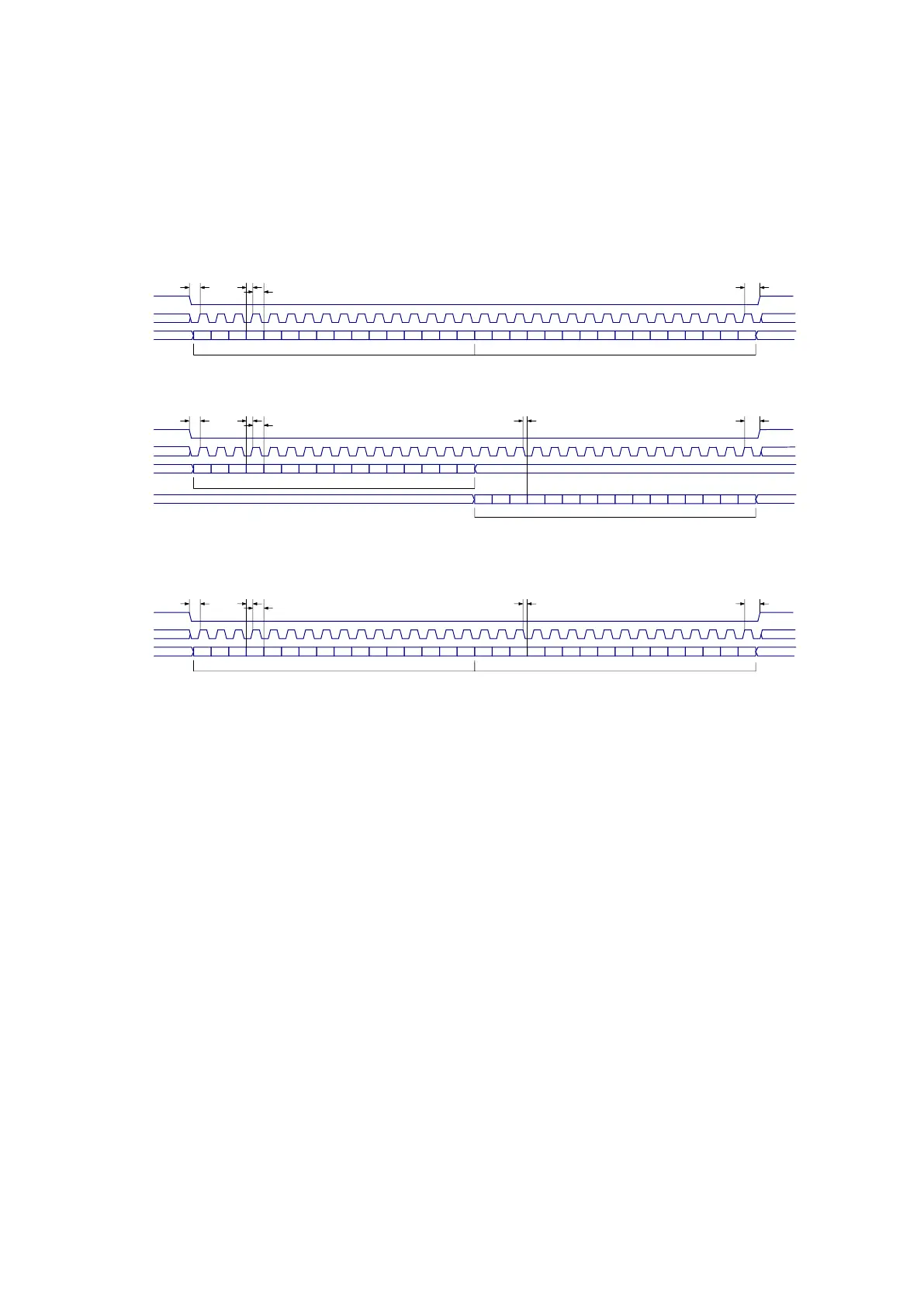

Write/read cycle waveforms are shown in Figure 1, Figure 2 and Figure 3. Note that

write operation is the same for both 3-wire and 4-wire modes. Although not shown in the

figures, multiple byte write/read is possible by repeating instruction/data sequence while

keeping SEN low.

SCLK

Don’t care

SEN

SDIO

Don’t care A141 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Write instruction Data

Don’t care

Don’t care

t

ES

t

DS

t

DH

t

EH

Figure 1 SPI write cycle, 3-wire and 4-wire modes

SCLK

Don’t care

SEN

SDIO

Don’t care A140 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

Read instruction

Don’t care

Don’t care

t

ES

t

DS

t

DH

t

EH

SDO

Don’t care

Output Data

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Don’t care

t

OD

Figure 2 SPI read cycle, 4-wire mode (default)

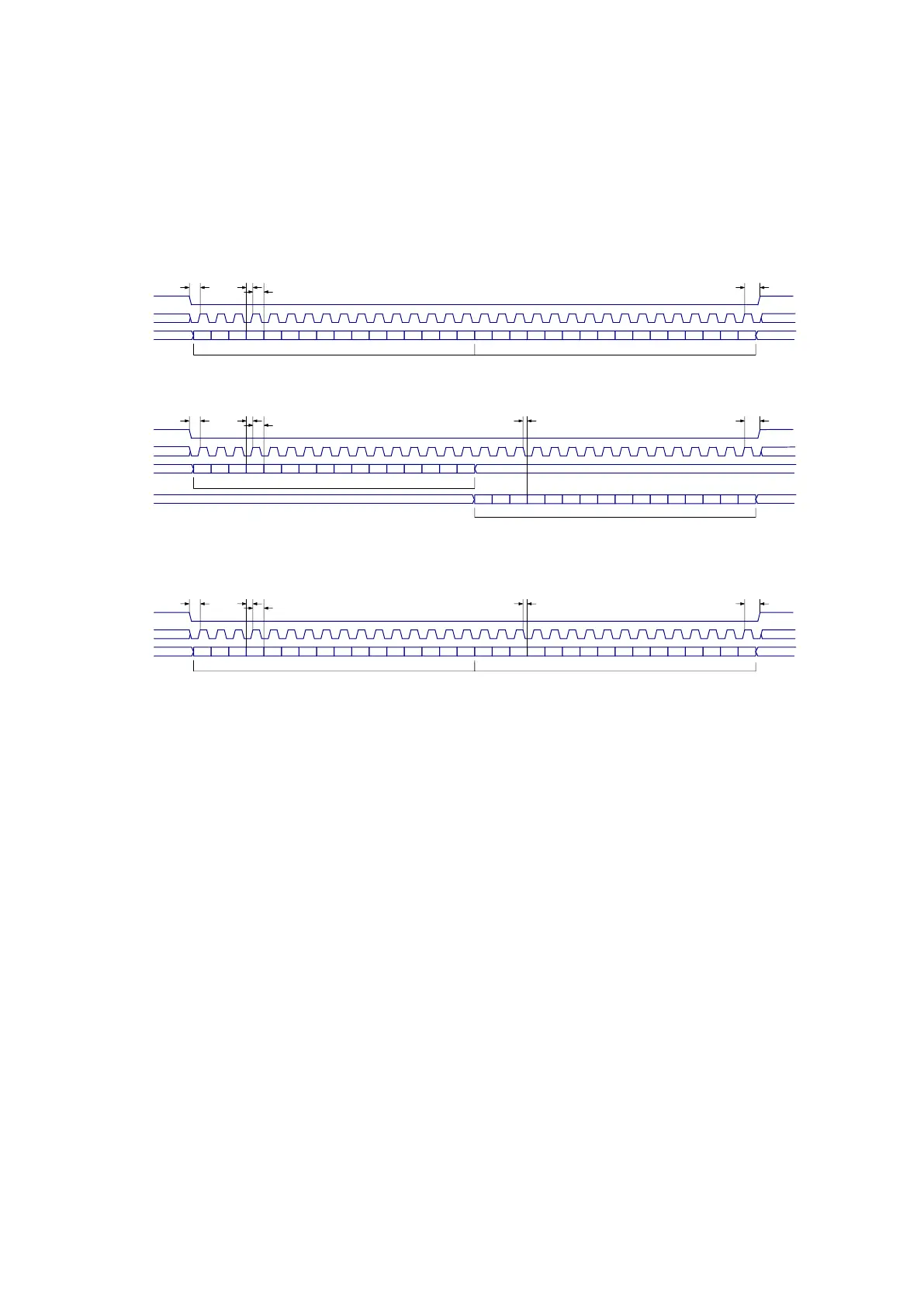

SCLK

Don’t care

SEN

SDIO

Don’t care A140 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

Read instruction

Don’t care

t

ES

t

DS

t

DH

t

EH

Output Data

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Don’t care

t

OD

Figure 3 SPI read cycle, 3-wire mode

Loading...

Loading...